NUC-140 Embedded ARM Cortex-M0 Platform

- NUC-140 Embedded System is a 32-bit ARM Cortex-M0 based platform optimized for real-time digital signal processing and instrument emulation using embedded FFT engines.

- It integrates high-speed ADCs, multiple communication interfaces, and efficient timer/PWM controls to support applications like portable oscilloscopes and spectrum analyzers in resource-constrained designs.

- Its software-emulated floating-point arithmetic and prime-factor FFT algorithm reduce computational load significantly, enabling approximately 3k transforms per second even with limited hardware resources.

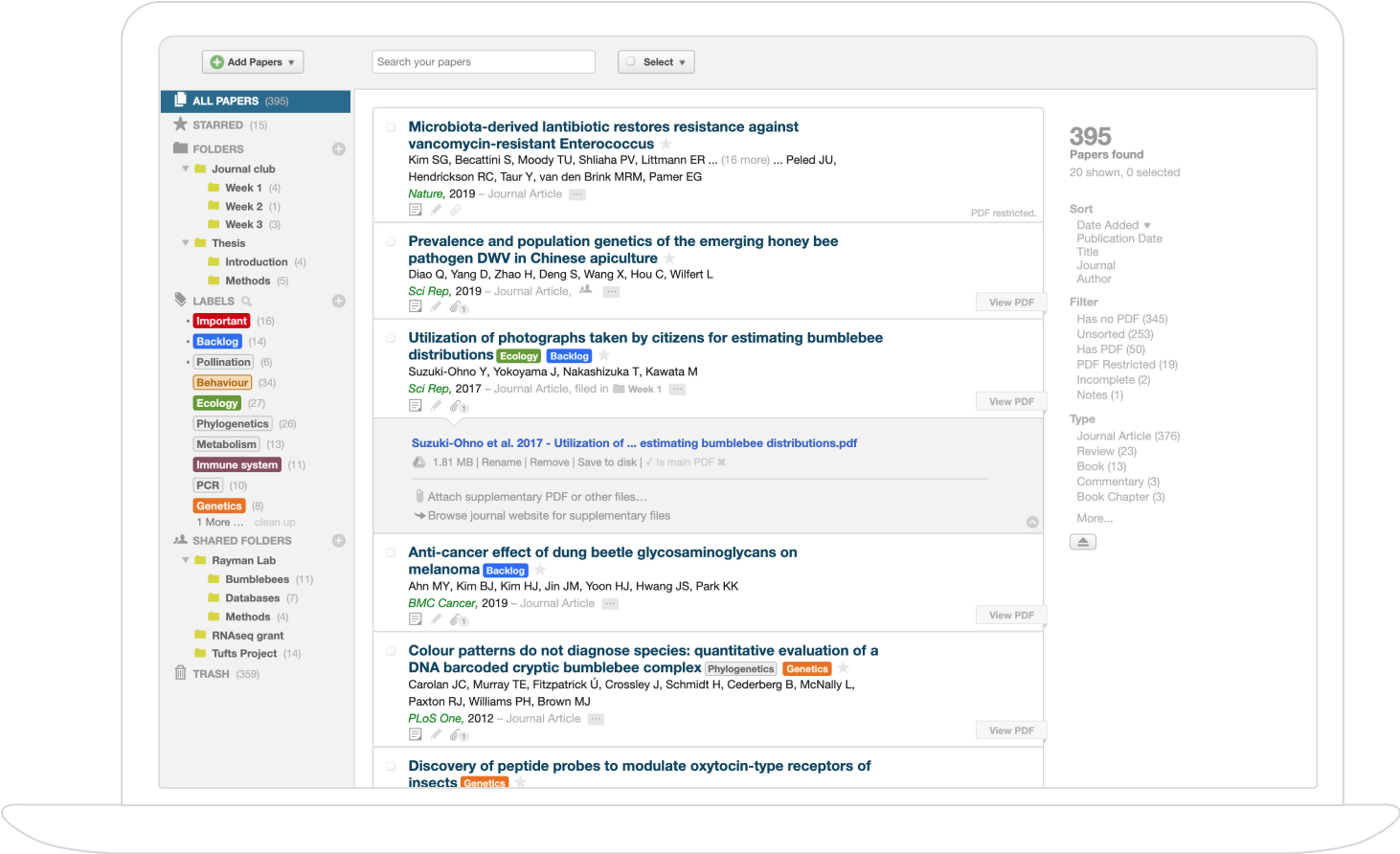

The Nuvoton NUC-140 represents a 32-bit ARM Cortex-M0 embedded platform designed for real-time digital signal processing, device interface, and instrumentation. Notable for its constrained on-chip resources and absence of hardware floating-point support, it forms the hardware foundation for both specialized digital spectral analysis (e.g., embedded FFT engines) and instrument emulation, such as portable digital oscilloscopes.

1. Hardware Architecture and System Resources

The NUC-140 microcontroller features a 32-bit ARM Cortex-M0 CPU operating up to 50 MHz, with core benchmarking typically at 22 MHz in reference implementations. Key specifications include:

- Flash ROM: 32 KB–64 KB on-chip

- SRAM: 4 KB–16 KB on-chip, depending on package variant

- ADC: 12-bit SAR, 8 single-ended channels (supporting 4 differential pairs), conversion time ≈1.2 µs at 22 MHz

- Timers: 3×16-bit general-purpose, PWM channels (used for signal generation)

- Communications: UART0–2 (115200 baud typical, 16-byte FIFO), SPI (LCD interface), I²C

- GPIO: Up to 48 pins, multiplexed for ADC, keypad, and trigger functionality

- Clocking: 22.1184 MHz internal RC oscillator and external crystal input, configurable with PLL and divisors:

- , as determined by TRM

DMA is not supported in the NUC-140 series, necessitating software-based buffer transfers. No hardware FPU is present; all floating-point arithmetic is emulated in software, which impacts performance for DSP workloads (Vernon et al., 18 Jan 2025, Romero et al., 23 Dec 2025).

2. Signal Acquisition: Analog and Digital Front-End

The ADC subsystem offers eight 12-bit inputs with a typical input impedance ≈100 kΩ. Differential input mode requires channel pairing (even as V+, odd as V–). Sampling throughput is controlled by configuring the internal clock and prescaler:

- ADC Clock:

- Sampling Rate: (each conversion ≈14 clock cycles)

In the oscilloscope setting, a maximum reliable sample rate ≈0.5 MS/s per channel (using CLKDIV=3) is achieved, with higher rates causing ISR bottlenecks and data corruption. Practical bandwidth is tested up to ≈300 Hz, the limiting factors being buffer transfer and display refresh, rather than analog design (Romero et al., 23 Dec 2025).

Signal conditioning uses direct BNC probe inputs (1 kΩ pull-down, no active buffer) and supports a built-in calibration square wave signal generated by PWM (2.5 kHz, formula: ).

3. Digital Signal Processing: FFT Engine and Prime-Factor Algorithm

A reference implementation targets a 36-point DFT using the prime-factor algorithm (PFA), exploiting co-prime factors (4×9) to reduce computational complexity. Discrete Fourier Transform is defined:

For , indices are mapped as , . The PFA structure allows decomposition:

PFA-36 computational cost is substantially lower than direct DFT: 560 real additions and 256 multiplications versus 2592 adds and 5184 mults—corresponding to approx. 78% and 95% reductions, respectively (Vernon et al., 18 Jan 2025). The implementation uses lightweight C kernels, small precomputed twiddle tables, and in-place buffer mapping to maximize cache locality under SRAM constraints.

4. Peripheral Integration and Embedded Instrumentation

The platform enables instrument-class peripherals:

- LCD Interface: ST7565R-compatible, 128×64 pixels, addressed as 8 pages × 132 columns for SPI-based framebuffer transfer. Example framebuffer layout:

Pixel plotting is achieved via bit-masked column operations, optimized for direct SPI writes.1 2 3 4

typedef union { uint8_t u8_col[8][132]; uint8_t u8_data[8*132]; } lcd_display_t;

- Keypad Matrix: 3×3 design using GPIO for row/column multiplexing, decoded using custom scanning routines to minimize debounce and ghosting errors.

- Trigger System: Supports auto, rising/falling edge, and single-shot using GPIO interrupts (e.g., GPA_0 routed via GPAB_IRQn), state-managed via firmware state machines with clear separation of ARM, TRIGGERED, DONE, and DISPLAY modes.

- Oscilloscope Probe Interface: Daughter-board with BNC inputs, jumpers for ADC channel routing, and optional calibration trace. Signal attenuation is limited to 1:1 due to analog non-linearities; attempts at higher attenuation result in distortion (Romero et al., 23 Dec 2025).

5. Real-Time Performance, Bottlenecks, and Memory Constraints

Performance measurement for the FFT application (22 MHz core, –O2 compiler) indicates:

| Stage | Real Adds | Real Mults | Cycles |

|---|---|---|---|

| 9× FFT-4 | 144 | 0 | ≈1 600 |

| 4× FFT-9 | 416 | 256 | ≈4 200 |

| Permute/Copy | – | – | ≈1 200 |

| Total | 560 | 256 | ≈7 000 |

FFT throughput achieves ≈0.32 ms/transform, enabling ~3 k transforms/s. For oscilloscope applications, the total system cycle budget for acquisition and display is ≈26 ms (primarily limited by UART transmission time), suggesting a real-time update rate ≈38 Hz (Vernon et al., 18 Jan 2025).

SRAM pressure is alleviated by careful buffer sizing (2×288 bytes for input/output in FFT mode), compact twiddle storage, and in-place computation. Code occupies ≈9 KB flash; all working buffers fit within the 4–16 KB SRAM envelope.

6. Accuracy, Validation, and Design Challenges

FFT output is validated against double-precision MATLAB DFT:

- Maximum normalized magnitude error <

- Frequency estimation error <0.1%

Oscilloscope measurement fidelity is limited by ENOB ≈10 (dominated by noise floor and GPIO leakage). Notable challenges include:

- No DMA: All peripheral-to-memory transfers must be interrupt- or polling-driven.

- SRAM Size: In-place computations and compact code/data structures are required.

- Floating-point Emulation: Floating-point arithmetic incurs significant performance penalty; floating used for algorithmic clarity.

- ADC Limitations: Safe operation of the ADC ISR at high sample rates requires careful tuning (minimum CLKDIV=3) to avoid data loss.

- Analog Front-End: Lacks true instrumentation buffer for high-Z or attenuated probing; performance degrades for >1:1 probe settings.

Interrupt routine starvation under heavy load is avoided by replacing ISRs with timer-flagged polling loops. Differential ADC operation requires small DC offsets (~100 mV) to suppress baseline spikes (Vernon et al., 18 Jan 2025, Romero et al., 23 Dec 2025).

7. System Integration, Replication, and Application Scope

The NUC-140, combined with external daughter-boards (BNC, keypad matrix, probe routing), supports cost-effective instrument replication. Software is typically built with Keil-ARM or GNU-ARM toolchains. The firmware is organized to enable rapid mode switching (trigger, scale, calibration) and modular initialization (clock, keypad, LCD, ADC, PWM, GPIO).

Applications of the NUC-140 platform as documented include:

- Embedded spectrum analyzers for communications, radar, control, and neural networks (Vernon et al., 18 Jan 2025)

- Portable oscilloscopes with ≈90% functionality of standard benchtop instruments (automatic, edge-triggered capture, waveform scaling, in-situ calibration) (Romero et al., 23 Dec 2025)

Limitations are primarily in sampling bandwidth and lack of deep memory when compared to commercial high-end oscilloscopes. Nonetheless, the NUC-140 demonstrates the viability of real-time, low-latency embedded DSP instrumentation under severe hardware resource constraints.