Reversible Transformer Blocks

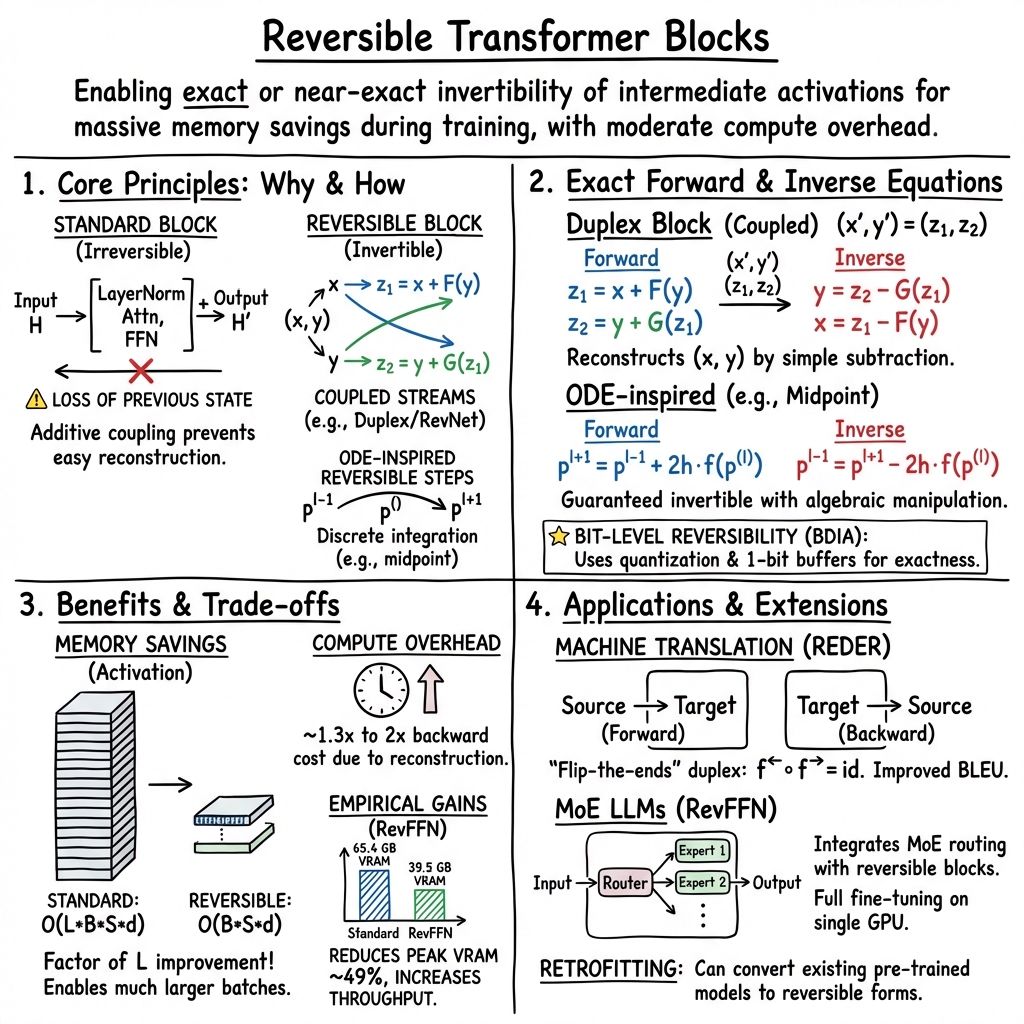

- Reversible Transformer Blocks are defined by invertible updates that reconstruct intermediate activations, reducing the memory footprint of deep architectures.

- They employ strategies like coupled streams, ODE-inspired steps, and RevFFN designs to replace non-invertible residuals, ensuring precise backward inversion.

- Their application yields significant memory savings and increased batch sizes in NLP and vision benchmarks, with a modest increase in compute during backpropagation.

Reversible Transformer blocks are special architectural components within the Transformer family designed to enable exact or near-exact invertibility of intermediate activations during forward and backward propagation. By structuring their computation around invertible update rules—often inspired by concepts from differential equations or carefully-coupled functional flows—these blocks allow the reconstruction of previous hidden states during backward passes rather than storing them, yielding substantial memory savings at the cost of moderate compute overhead. Multiple designs have been proposed and evaluated across core NLP and vision benchmarks, including parameter-efficient models for sequence-to-sequence learning as well as scalable blocks for LLMs and Mixture-of-Experts (MoE) architectures.

1. Core Principles and Block Mechanisms

Standard Transformer blocks—comprising Layer Normalization (LayerNorm), Multi-Head Self-Attention, and Feed-Forward Networks (FFN), interleaved by residual additions—are fundamentally irreversible due to the additive coupling and loss of input after each residual step. In contrast, reversible Transformer blocks replace these steps with bijective constructions, typically organized as coupled updates on a split hidden state, integration-inspired recursions on sequences, or explicit bidirectional flows.

Common reversible block frameworks include:

- Coupled Streams (Classic "Duplex"/RevNet style): The hidden state is split into two streams, with each alternately updated via injective functions, allowing forward and inverse mapping by simple subtraction and function reuse. In REDER, a Reversible Duplex Transformer layer operates on , updating via

The inverse is

Functions and encapsulate layer-norm, multi-head attention, or FFN operations (Zheng et al., 2021).

- Reversible FFN for MoE LLMs: The input tensor splits into , and cross-branch attention/MLP is applied in a sequence that is algebraically invertible; specifically,

The inversion reconstructs and then via fixed-point iteration when necessary (Liu et al., 24 Dec 2025).

- ODE-inspired Reversible Steps: Some designs treat the block update as a discrete integration of an ODE, employing schemas such as explicit midpoint or leapfrog updates:

These are exactly invertible by algebraic manipulation, and can be retrofitted to existing architectures for maximal compatibility (Gal et al., 27 Nov 2025). The BDIA approach introduces random bidirectional integration with per-block , yielding

with activation quantization and 1-bit side-channel to ensure bit-level reversibility (Zhang et al., 2024).

2. Exact Forward and Inverse Equations

Reversible block definitions differ depending on the underlying principle:

- Duplex Blocks: The forward and inverse are given explicitly with parameter sharing:

No extra memory or weights are necessary for inversion since and are reused (Zheng et al., 2021).

- RevFFN for MoE: The forward and backward rules are:

A single fixed-point iteration for suffices for practical inversion accuracy (Liu et al., 24 Dec 2025).

- Integration-based (Midpoint, Leapfrog, Hamiltonian): For the explicit midpoint,

These updates are guaranteed invertible under mild smoothness and step-size restrictions (Gal et al., 27 Nov 2025). BDIA updates support bit-level exact inversion with quantization and 1-bit buffers (Zhang et al., 2024).

3. Memory, Computational Complexity, and Practical Gains

Reversible transformer blocks achieve substantial activation memory savings relative to conventional Transformers:

- Standard Transformers: For layers, batch size , sequence length , and model dimension , the activation storage is due to caching all intermediate activations for gradient computation.

- Reversible Architectures: Only the input and output (and/or small buffers) need retention, yielding storage, a factor of improvement. This enables 10–20 larger batches in practice, particularly pronounced with deep models (e.g., –96) (Gal et al., 27 Nov 2025, Zhang et al., 2024).

- Compute Overheads: The backward pass must reconstruct hidden states by forward-evaluating the block functions, resulting in an overall backward compute cost of approximately $1.3$ to standard transformers, depending on the inversion variant and fixed-point iterations used (Liu et al., 24 Dec 2025, Gal et al., 27 Nov 2025).

- Empirical Results: RevFFN reduces peak VRAM by ~49% compared to SFT+activation checkpointing, and yields throughput improvements:

| Method | Peak VRAM (GB) | Throughput (samples/s) | |------------------|---------------|------------------------| | SFT + Checkpoint | 65.4 | 19.7 | | LOMO | 42.2 | 17.3 | | GaLore | 45.1 | 35.2 | | RevFFN | 39.5 | 24.6 |

4. Model Variants and Extensions

Reversible blocks have been adapted for multiple Transformer tasks and architectures:

- Machine Translation (REDER): A single reversible stack serves as both encoder and decoder, allowing "flip-the-ends" duplex translation. Forward (source-to-target) and backward (target-to-source) functions are exact inverses, providing . This yields +1.3 BLEU over multitask NAT, with empirical values of 27.50 BLEU (EnDe), 31.25 BLEU (DeEn) compared to multitask baseline 26.20/30.02 (Zheng et al., 2021).

- Mixture-of-Experts LLMs: RevFFN integrates MoE routing within reversible blocks using projection adapters, retaining full expert capacity for half-width streams while reducing memory requirements and permitting single-GPU full parameter fine-tuning (Liu et al., 24 Dec 2025).

- Retrofitting Existing Models: Integration-based reversible blocks permit conversion of established (irreversible) architectures via fine-tuning procedures. This employs scheme-specific recursions and distillation to minimize output drift while introducing near-lossless invertibility (Gal et al., 27 Nov 2025).

- Bit-level Reversibility: BDIA-transformers achieve exact reversibility by quantizing activations and storing per-block 1-bit buffers. The BDIA formulation treats each transformer layer as a numerical ODE step, switching between forward and backward schemes per sample and block, with expectation matching standard Euler and variance acting as a regularizer. Empirical studies show improved validation performance and minimal computational penalty (Zhang et al., 2024).

5. Comparative Landscape

- RevNet-type Coupling vs. Symplectic Integrators: RevNet-based methods (as in REDER and RevFFN) construct bijective coupling between split hidden state streams for layered invertibility (Zheng et al., 2021, Liu et al., 24 Dec 2025). Symplectic and midpoint-based approaches (BDIA, explicit midpoint, leapfrog) align block updates with invertible discretizations of dynamical systems, offering theoretical guarantees of volume preservation and time-reversibility (Gal et al., 27 Nov 2025, Zhang et al., 2024).

- Relation to Multi-task and Shared Encoder-Decoder Models: Standard multitask bilingual Transformers, which share parameters between an encoder and a decoder, suffer from interference and BLEU drops due to conflicting requirements in each translation direction. Reversible blocks, by contrast, support dual specialization at each end, provably ensuring on the continuous representations and eliminating performance loss from parameter co-usage (Zheng et al., 2021).

- Comparison to Checkpointing and PEFT: Reversible blocks halve activation memory compared to naïve checkpointed full fine-tuning and can outperform existing memory-efficient methods (LOMO, GaLore), with only moderate throughput penalty owing to one extra recomputation per layer (Liu et al., 24 Dec 2025).

6. Implementation, Deployment, and Practical Considerations

Key aspects of practical deployment include:

- Parameter Sharing: Perfect invertibility is achieved by reusing function parameters in both forward and inverse directions. No overhead in parameter count is introduced (Zheng et al., 2021, Liu et al., 24 Dec 2025).

- Inversion Algorithms: For simple coupling layers, algebraic inversion suffices. Cross-branch attention in RevFFN requires one step of fixed-point iteration, which yields error well below machine epsilon.

- Framework Integration: In PyTorch/HuggingFace environments, reversible layers are implemented by replacing

forwardwith invertible sequences and registering custom autogradbackwardhooks that trigger on-the-fly inversion (Liu et al., 24 Dec 2025). - Two-stage Training for MoE Integration: Adapter "warm-up"—freezing backbone experts and MoE router—stabilizes early training of projection adapters, followed by joint fine-tuning (Liu et al., 24 Dec 2025).

- Quantization for Exactness: BDIA-transformers need to quantize activations and store 1-bit buffers (for low-order quantization error) to support exact reversibility. The overhead is negligible compared to activation memory savings, and standard architecture is restored at inference by setting (Zhang et al., 2024).

- Empirical Hyperparameters: For ODE-style blocks, step size ( or ) and fixed-point depth () should be tuned for the application, with and modest quantization depth (–9) working well in practice (Gal et al., 27 Nov 2025, Zhang et al., 2024).

7. Experimental and Theoretical Implications

Reversible Transformer blocks deliver activation memory reductions scaling with network depth while preserving or slightly improving performance on major benchmarks—demonstrated across vision and language tasks:

- ViT-small with BDIA: Activation memory reduced by , with improvement in validation accuracy (Zhang et al., 2024).

- Nano-GPT2: Similar reduction in memory with negligible perplexity impact (Zhang et al., 2024).

- GPT-2/TinyLlama/SmolLM2 (Reversible): Throughput and memory benchmarks show 10–20 batch size increases, 20–100% throughput gain at 30–50% extra compute, and quality within of standard (Gal et al., 27 Nov 2025).

- MT BLEU (REDER): +1.3 BLEU over multitask NAT, with theoretical invertibility in dual translation (Zheng et al., 2021).

- MoE LLMs (RevFFN): Maintains or improves performance over LoRA, SFT, and PEFT baselines, with 49% less VRAM than checkpointing (Liu et al., 24 Dec 2025).

These results confirm that reversible Transformer blocks constitute a scalable solution for memory-efficient training and inference in deep sequence models, while providing theoretical guarantees rooted in injectivity and time-reversible numerical frameworks. The ability to retrofit pre-trained models into reversible forms extends their applicability to resource-constrained environments without architectural overhaul.