A digitally controlled silicon quantum processing unit

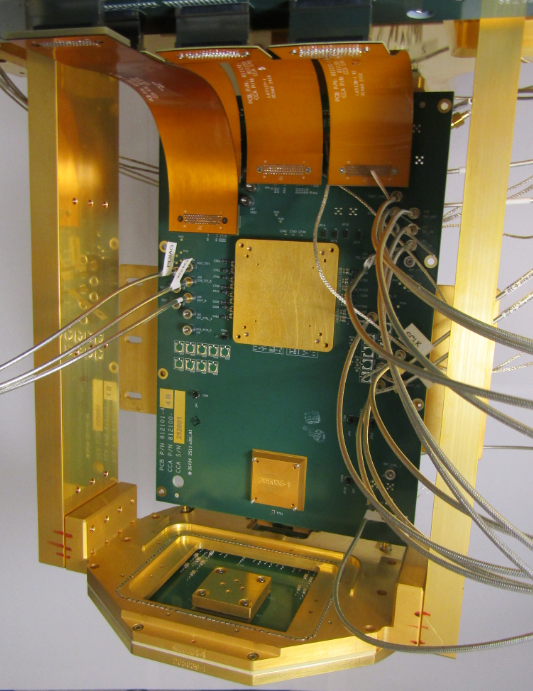

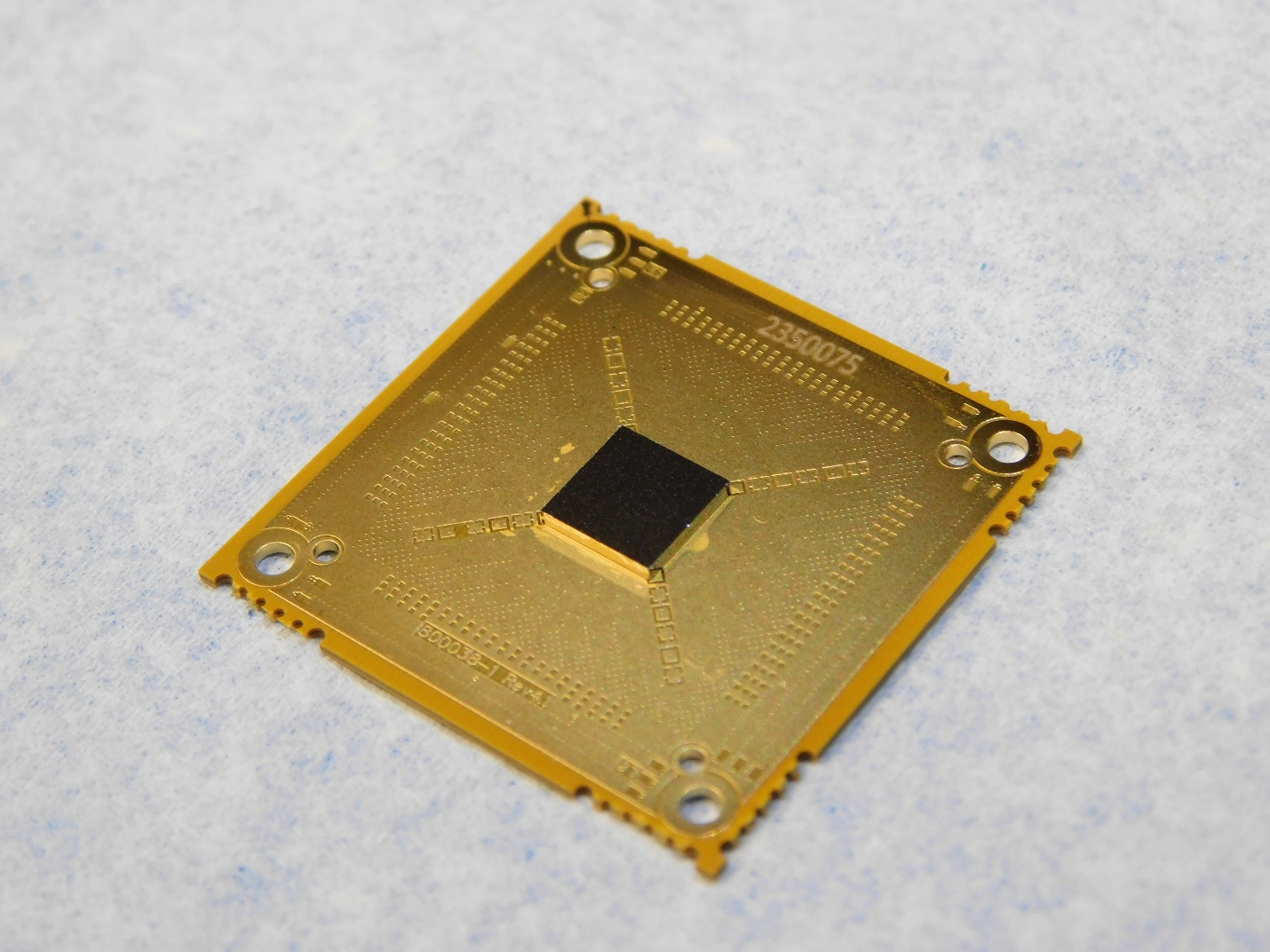

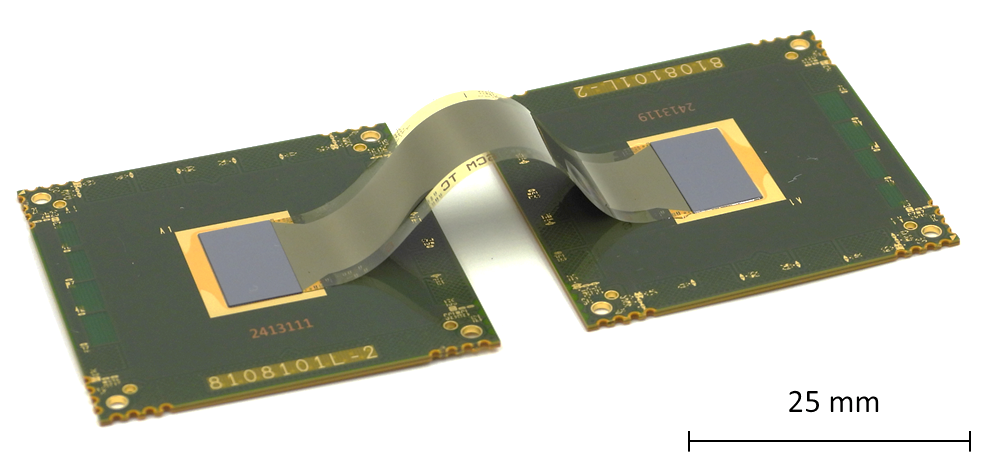

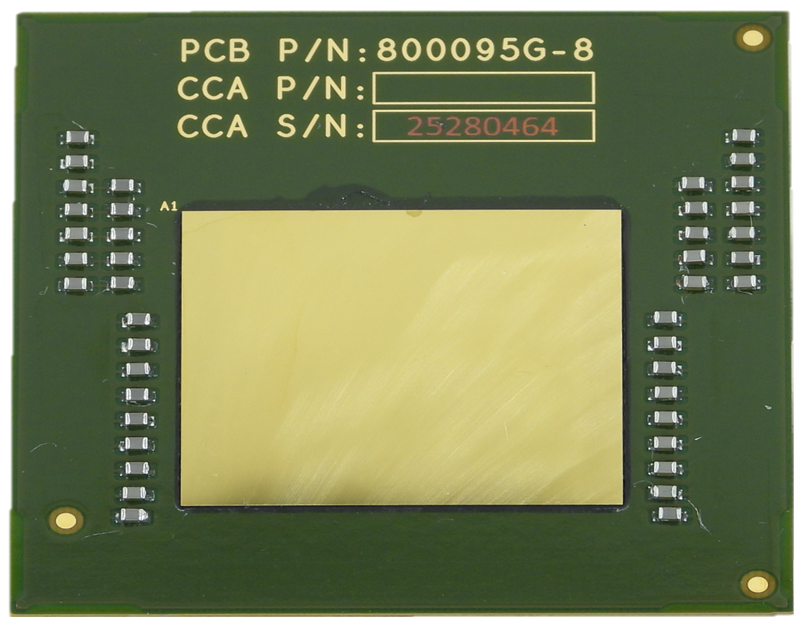

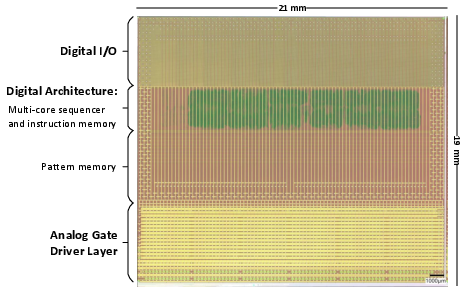

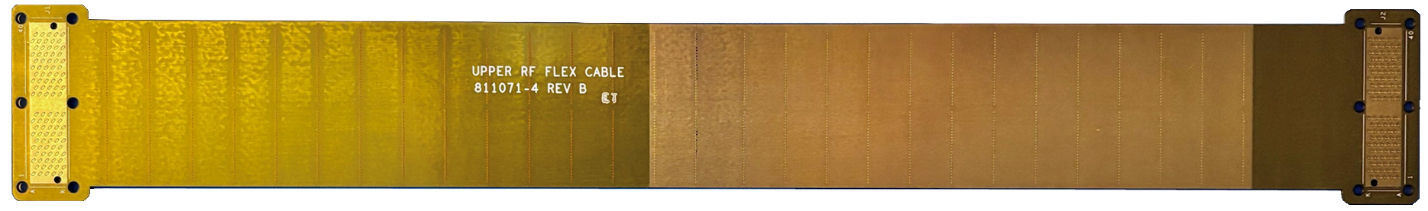

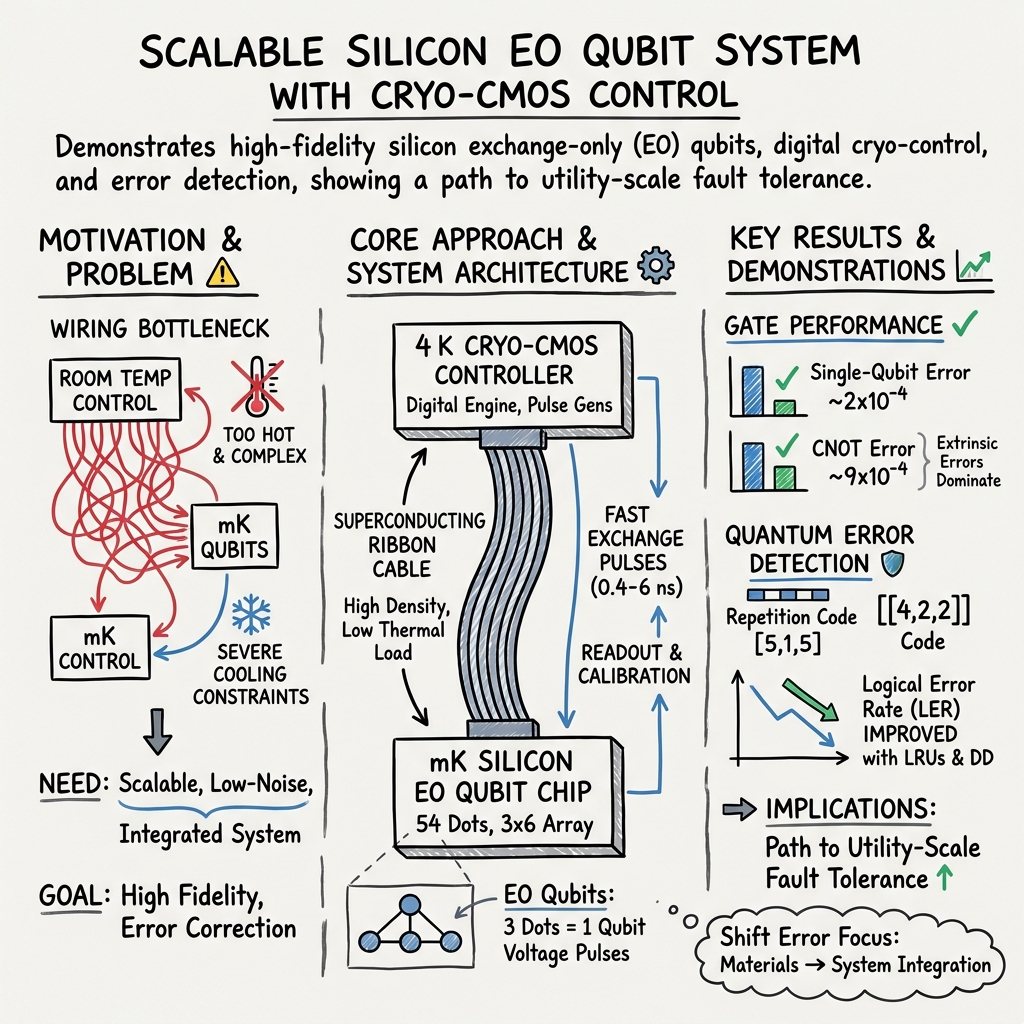

Abstract: Commercially-relevant quantum computers will require large numbers of high-performing qubits that can be manufactured, integrated, and controlled at scale. Silicon exchange-only (EO) qubits are a strong candidate modality due to their control-signal simplicity and compatibility with advanced semiconductor manufacturing, but questions remain around the achievability of sufficiently low noise and a scalable control and wiring solution. Here we introduce a quantum processing unit composed of a custom-designed cryogenic CMOS controller, a novel high-density superconducting ribbon cable, and a low-noise EO qubit device. The quantum chip features a three-rail array of 54 exchange-coupled quantum dots, configurable to host up to 18 EO qubits. We integrate and use these components to demonstrate qubit performance for both single-qubit and entangling operations that advances the EO state of the art by an order of magnitude. We further validate this system by implementing a distance-5 repetition code and a quantum error detecting code then make detailed comparisons with simulations. Our approach facilitates a utility-scale quantum computer with manageable operational and capital requirements.

Paper Prompts

Sign up for free to create and run prompts on this paper using GPT-5.

Top Community Prompts

Explain it Like I'm 14

A simple guide to “A digitally controlled silicon quantum processing unit”

1) What is this paper about?

This paper shows a working “mini quantum computer” made from silicon—similar to what regular computer chips use. It combines:

- a very cold silicon chip that holds quantum bits (qubits),

- a special control chip that runs at 4 kelvin (about −269°C),

- and a tiny superconducting ribbon cable that links them.

Together, they form a quantum processing unit (QPU) that can run small error-correcting programs. The big idea is to prove that silicon qubits can be controlled in a practical, factory-friendly way that could scale up to useful quantum computers.

2) What questions were the researchers trying to answer?

They focused on three main questions:

- Can we make silicon qubits that are quiet (low noise) and accurate enough for serious computation?

- Can we control many qubits without tons of bulky wires and power-hungry gear at room temperature?

- Can this system actually run error-checking routines (the backbone of reliable quantum computing), not just single, simple qubit tricks?

3) How did they do it?

Think of the system like a music band where each part must stay in sync:

- The qubits (the instruments): Each qubit is made from three electrons trapped in three tiny “quantum dots” in silicon. Electrons act like tiny magnets (spins). Instead of using microwaves or big magnets, the team controls qubits by nudging electrons closer or farther with fast voltage pulses—like telling the musicians exactly when to swap places. This style is called “exchange-only” because it uses the exchange interaction (electrons briefly “swap” to perform a gate).

- The cold control chip (the conductor): A custom-made CMOS control chip runs at 4 K inside the refrigerator. It generates fast, precisely timed voltage pulses that tell each qubit exactly when and how to “swap.” Running it cold saves power and keeps signals clean, while avoiding a messy forest of wires from room temperature.

- The superconducting ribbon (the quiet cable): A thin, high-density superconducting ribbon cable connects the 4 K controller to the even colder qubit chip (at millikelvin temperatures). It carries many signals with almost no heat leakage and very little signal cross-talk—like a smooth, multi-lane highway that doesn’t warm up the destination.

- The quantum chip (the stage): The silicon chip has 54 quantum dots arranged in three lines (rails) and can host up to 18 qubits. It’s built using semiconductor manufacturing techniques, which is good news for making lots of them reliably.

- The tests (the performance): They checked basic gate quality (single- and two-qubit operations), then ran small error-correcting routines called repetition codes (distance-3 and distance-5) and a quantum error-detecting code called [[4,2,2]]. They also compared real results to simulations to understand what’s causing errors.

Helpful analogies:

- Exchange-only gates: like choreographed swaps in a dance—no need for fancy lighting (microwaves), just precise timing.

- Dynamical decoupling: like remixing steps so background noise averages out.

- Leakage reduction units (LRUs): like a bouncer that checks if a dancer wandered off-stage and puts them back where they belong.

4) What did they find, and why is it important?

Main results:

- Much better gate accuracy: Single-qubit error rates around 0.02% and two-qubit CNOT gates around 0.3% on average, with best CNOT near 0.09%. That’s about 10× better than earlier work with this qubit type. Better gates mean fewer errors for error correction to handle.

- Low intrinsic noise in the devices: The silicon structures themselves are quiet, thanks to careful materials engineering (like using isotopes that reduce magnetic “static”). The team’s measurements suggest most remaining errors come from “extrinsic” factors, such as tiny calibration mistakes or static magnetic field gradients, not from the qubits’ fundamental limitations.

- Working error-checking circuits:

- Distance-5 repetition code (using 7 qubits) showed low logical error rates and improved reliability compared to distance-3, as expected.

- They used LRUs to keep “leakage” (leaving the qubit’s intended state space) under control, and showed that without LRUs, problems build up over time.

- The [[4,2,2]] quantum error-detecting code (using 6 qubits) reached about 95% logical fidelity after three rounds when they kept only runs with no detected errors (post-selection). Without using the error signals, the fidelity dropped to ~59%, showing the code truly detects and filters out errors.

- Simulations match the data: Their models agreed closely with experiments. That’s a big deal—it means they understand where the errors come from and how to predict system behavior as it grows.

Why this matters:

- Controlling many qubits is one of the hardest parts of building a useful quantum computer. This work shows a realistic way to do it—by moving smart, low-power control closer to the cold qubits and linking them with a superconducting cable.

- The accuracy gains and working error-check routines suggest silicon exchange-only qubits are strong candidates for scaling up.

5) What’s the big takeaway?

The team built and tested a full, integrated silicon quantum processing unit with:

- factory-friendly chip technology,

- energy-efficient, cryogenic digital control at 4 K,

- a high-density superconducting link to the ultra-cold qubit chip,

- and record-setting performance for this qubit style.

It’s a practical blueprint for larger, commercial quantum computers that fit into a single cryostat (ultra-cold fridge). Next steps include refining power per qubit, improving chip uniformity, and further tightening calibration and magnetic cleanliness. But the core message is optimistic: this approach looks technically sound, scalable, and commercially reasonable—bringing useful quantum computing closer to reality.

Knowledge Gaps

Knowledge gaps, limitations, and open questions

Below is a single, concrete list of what remains missing, uncertain, or unexplored, framed so that future work can act on each item.

- Controller-induced errors: The dominant “extrinsic” errors (static magnetic field gradients and contextual pulse miscalibration) are asserted but not decomposed or quantified; a channel-by-channel budget for timing skew, edge jitter, amplitude error, and cross-talk contributions to exchangle miscalibration is needed, alongside mitigation strategies (e.g., active deskew, calibration-in-the-loop).

- Error spikes: The as-yet unexplained “spikes in detection events” seen in the distance‑5 repetition code remain unresolved; their temporal structure, environmental correlations (vibration, EMI, temperature), and coupling to controller/ribbon activity must be diagnosed.

- Calibration stability: Long-term drift (hours–days) and thermal-cycle robustness of qubit and controller calibrations are not reported; quantify stability and re-tune overhead for sustained QEC operation.

- Idle decoupling trade-offs: The impact of full-permutation dynamical decoupling on non-target qubits and on two-qubit gate fidelity (noted degradation under global decoupling) lacks a systematic study; characterize scheduling rules and spectral interference under high parallelism.

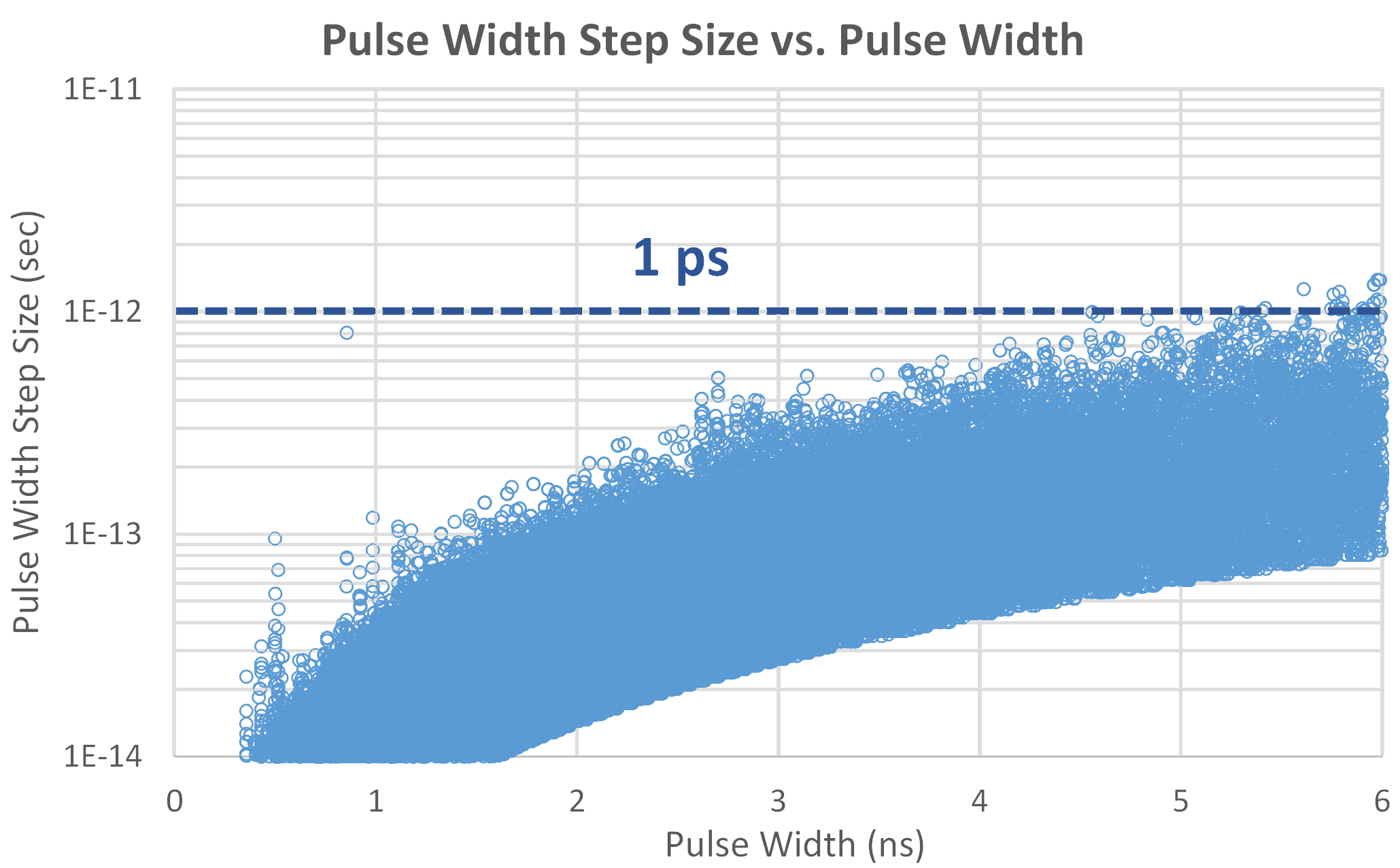

- Pulse timing fidelity: Jitter and skew at the qubit for sub‑ns pulses (per channel and across 150+ channels), and their direct contribution to gate error, are not measured; implement timing metrology at mK and assess deskew requirements.

- SPAM metrics: Per-qubit state-preparation and measurement (SPAM) error rates, latencies, and readout-induced cross-talk are not provided; supply a full SPAM budget and its scaling with the number of sensors.

- In-cryostat digitization: Readout is digitized at room temperature; the performance, power, and thermal impact of cryo-ADCs (and their effect on total wiring and latency) are untested in this system.

- Real-time feedforward: No demonstration of low-latency measurement-conditioned control (branching) is provided; end-to-end latency from measurement to actuation and controller support for conditional instructions must be specified and verified.

- QEC beyond detection: Only error detection is shown ([[4,2,2]] with postselection); active error correction with real-time decoding and corrective operations remains to be demonstrated.

- Decoding choices: Repetition code analysis uses a naïve parity decoder; quantify gains from optimal/near-optimal decoders and sensitivity to correlated errors (space/time), including realistic decoder latencies for online use.

- Leakage characterization: Leakage rates per operation and LRU success/failure probabilities are not quantified; measure leakage dynamics, optimize LRU sequences, and assess LRU-induced overheads on large circuits.

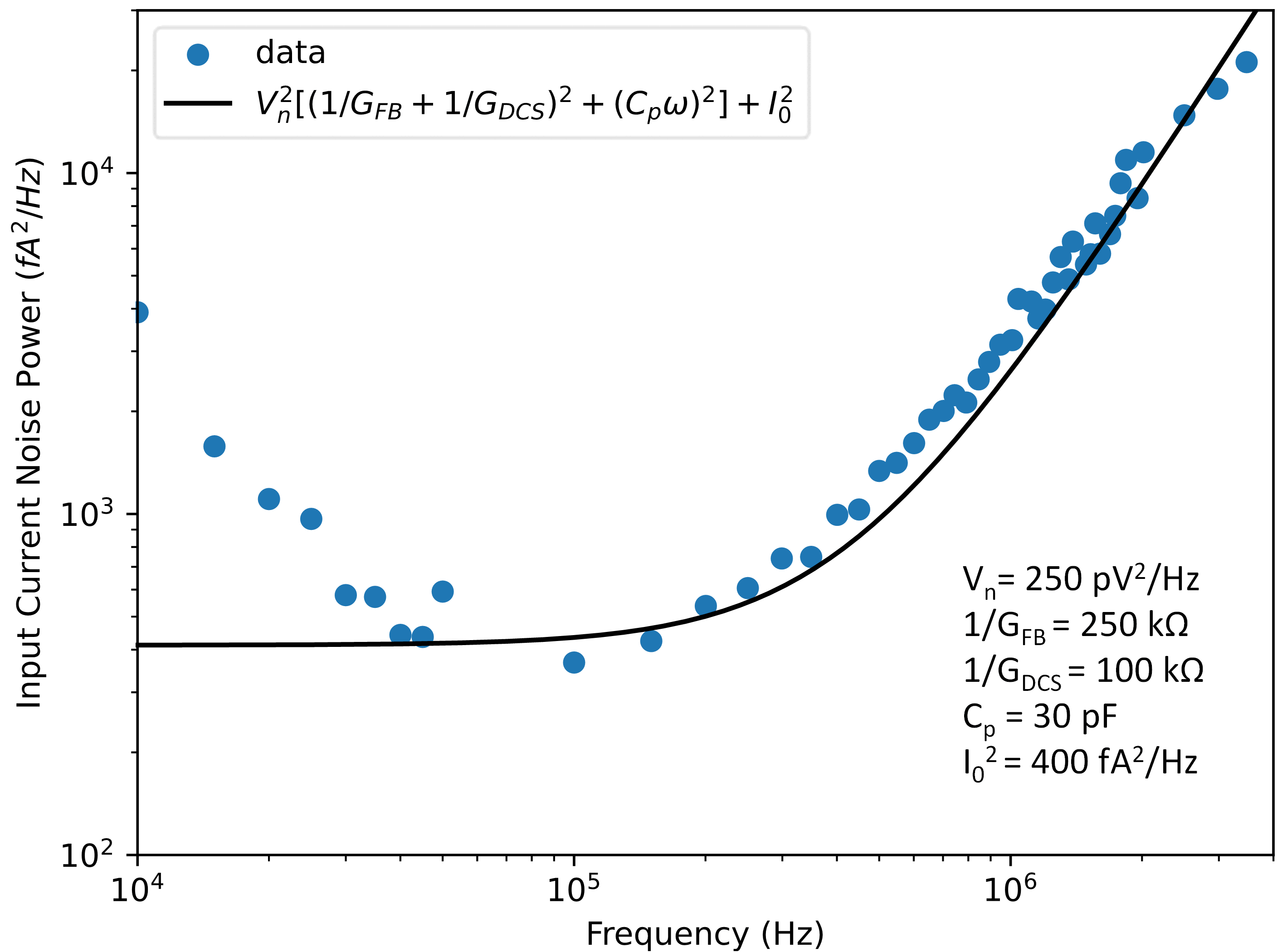

- Intrinsic vs in-situ noise: Charge and magnetic noise are measured on a similar device via cryoMUX rather than in-situ on the integrated QPU; repeat intrinsic noise extraction in the full stack to isolate controller/interconnect contributions.

- Relaxation limits: No (relaxation) measurements or idling error budgets at (near) zero field are reported; measure vs temperature and field to bound idle error rates.

- Valley-splitting and uniformity: Valley splitting and its distribution across the array (and across wafers) are not presented; quantify its link to leakage and device-to-device variability.

- Magnetic hygiene at scale: Flux trapping, cooldown protocols, shielding efficacy, and spatial gradient management are not characterized for larger chips; define field cancellation tolerances and verify reproducibility across thermal cycles.

- Ribbon reliability: The superconducting ribbon’s mechanical and electrical reliability (e.g., after repeated thermal cycling, flexing, and handling) is untested; perform accelerated life tests and report failure modes.

- Far-end signal integrity: Only near-end crosstalk is reported (<−80 dB up to 10 GHz); far-end crosstalk/reflections at the mK load with package parasitics, inter-line skew, and simultaneous switching noise remain uncharacterized.

- Thermal headroom: While <10 μW is conducted to mK for this ribbon, the dependence on channel count and switching activity is not measured; provide thermal models/measurements for scaled systems and switching-heavy schedules.

- Line-count scalability: 296 lines for up to 18 EO qubits implies challenging scaling; map a concrete path (e.g., multiplexing, hierarchical cryo-control, on-chip routing) to 103–106 qubits with quantified line counts and bandwidths.

- Power per qubit: Controller power is ≤3.5 W total, but per‑qubit/per‑channel power and a scaling law to thousands/millions of qubits are not provided; align with 4 K stage capacity of commercial cryostats.

- Program memory/throughput: The 6144-word instruction memory and pattern memories may limit circuit depth/complexity; quantify maximum cycle rates (round/s, shots/s), memory reuse/compression, and streaming options for deep, real-time QEC.

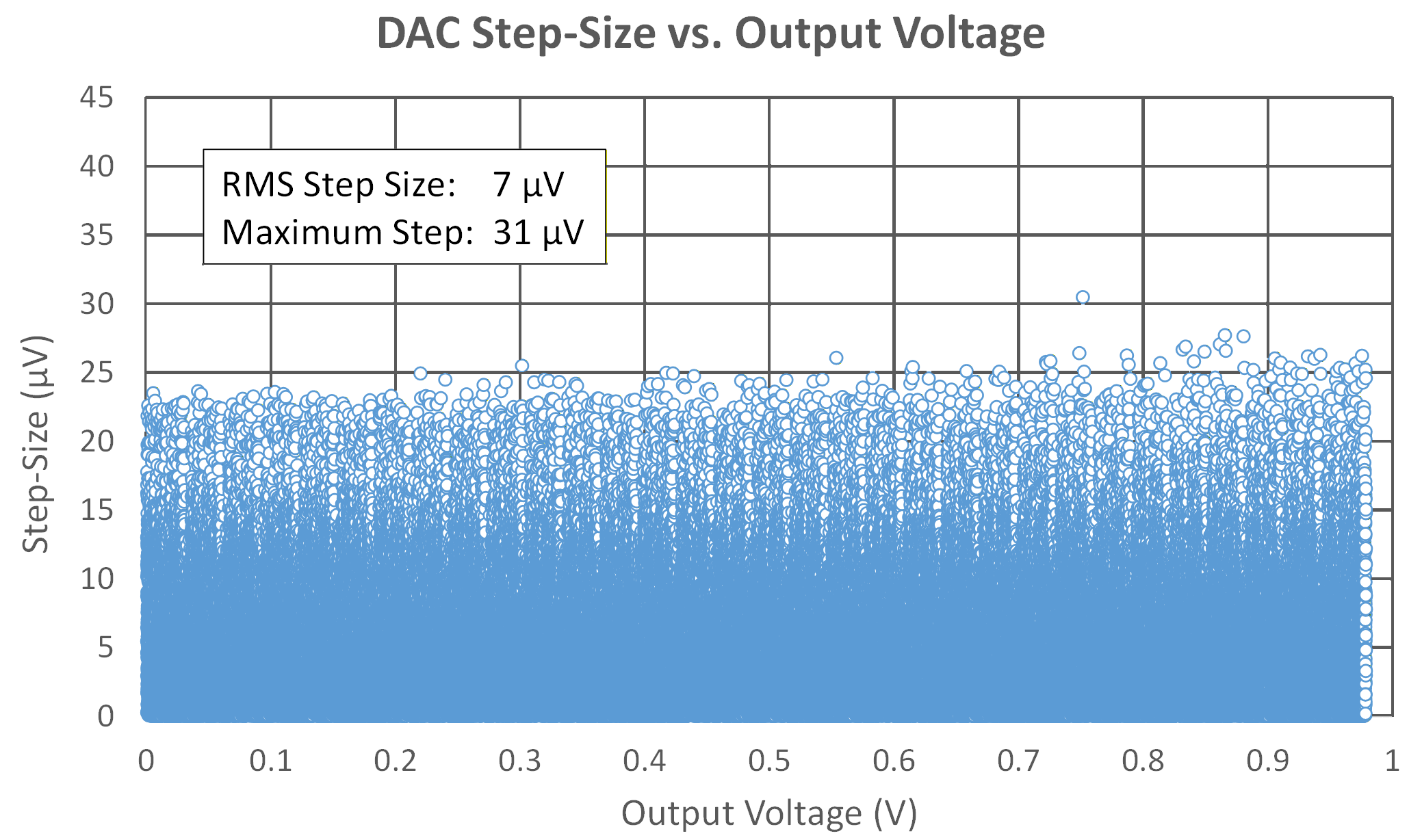

- Controller noise injection: Spectral density (including 1/f) of DAC/switch-induced noise at 4 K and its coupling to qubit electrodes via the ribbon/package are not quantified; measure and bound controller-originated charge noise.

- Channel variability: Channel-to-channel differences (output impedance, filter settings, edge rates) and their impact on uniform gate calibration are not reported; characterize variability and implement per-channel compensation.

- Full-array operation: Only subsets (6–7 qubits) of the 3×6 lattice are used; demonstrate full-lattice parallel operation with nearest-neighbor schedules representative of 2D surface-code cycles.

- Yield and distributions: Device yield, performance distributions (gate error, noise, SPAM) across the 54-dot array and across dies/wafers are not provided; report statistics and selection criteria affecting usable-qubit fraction.

- Backend routing: A “manufacturable interconnect and qubit back-end routing solution” is identified as future work; propose and validate specific multilayer BEOL stacks and crossing schemes with quantified parasitics and cross-talk.

- QEC cycle timing: The round duration (including gates, LRUs, readout, decode/actuate latency) is not reported; provide a full timing budget to assess compatibility with coherence and decoder hardware.

- System-level projections: Claims of single‑cryostat utility-scale viability lack quantitative projections (cost, footprint, thermal budgets) at target scales; furnish models connecting current metrics to system-level requirements.

- Field sensitivity: Operation at near-zero magnetic field is maintained via external coils; quantify sensitivity to ambient field drift and spatial gradients, and specify stabilization requirements for large-scale deployment.

- Logical operations in codes: The [[4,2,2]] implementation assesses fidelity after detection but does not demonstrate logical gates between encoded qubits; next steps should include fault-tolerant logical operations with detection/correction.

Practical Applications

Immediate Applications

The paper’s integrated QPU (4 K cryo-CMOS controller + superconducting ribbon cable + low-noise Si/SiGe exchange-only qubit chip) and validation experiments enable several deployable uses across sectors:

- Semiconductor/Quantum hardware: High‑channel‑count cryogenic control for spin‑qubit experiments

- Use: Replace room‑temperature AWGs and analog wiring with a compact 4 K mixed‑signal controller that generates all time‑varying qubit control (baseband pulses with ~150 ps edges, 400 ps–6 ns widths) and runs compiled programs autonomously.

- Tools/products/workflows: “Cryo control board” based on the described 130 nm RF CMOS ASIC; a qubit control compiler targeting the custom ISA; on‑chip PRNG‑enabled RB workflows.

- Dependencies/assumptions: Access to 4 K cryo‑CMOS ASICs or foundry PDKs characterized at cryo; power budget ≤~3.5 W per controller stage; digital comms and SPI integration; availability of high‑density decoupling capacitor assemblies.

- Semiconductor/Quantum hardware; Cryogenic instrumentation (astronomy, sensing): Superconducting Nb‑on‑polyimide ribbon cable for 4 K–mK interconnect

- Use: Deliver hundreds of high‑bandwidth, low‑crosstalk lines (296 coax lines, <-80 dB crosstalk up to 10 GHz) across a thermal standoff (<10 μW load to mK), avoiding room‑temperature wiring bottlenecks.

- Tools/products/workflows: Standardized cryogenic “ribbon backplane” and laminate adapters for mK modules; connectorized assemblies for dilution refrigerators and cryo‑instruments (TES/MKID arrays, superconducting qubits, quantum dots).

- Dependencies/assumptions: Availability of Nb‑on‑polyimide fabrication, reliable connectorization, mechanical robustness under thermal cycling, and EMI shielding compatible with sensitive devices.

- Academia/Quantum research: Benchmarking and validation workflows for small‑scale QEC readiness

- Use: Adopt distance‑3/5 repetition code and [[4,2,2]] error‑detecting code as standardized acceptance tests; measure logical error rate (LER), detector event fraction (DEF), and run detector‑error‑model (DEM) analyses to flag correlated errors.

- Tools/products/workflows: RB/BRB protocols tuned for exchange‑only (EO) qubits; naive parity decoders; DEM pipelines; experimental schedules with NZ1 full‑permutation dynamical decoupling for idling qubits; leakage‑reduction units (RIL sequences).

- Dependencies/assumptions: Availability of two‑qubit entangling gates and parallelism; readout chains (TIAs at 4 K, digitizers at room temperature); calibration pipelines for exchangle angles.

- Semiconductor fabrication/Foundries: Low‑noise Si/SiGe device stack and process integration

- Use: Implement isotopic enrichment (28Si, reduced 73Ge), engineered valley splitting, and BEOL stack with W vias and Nb CPW routing for low‑noise triple‑dot arrays; 200‑mm wafer probing and flip‑chip LGA packaging for yield screening.

- Tools/products/workflows: Process design kits (PDKs) with cryo‑relevant figures of merit; wafer‑level test recipes to select high‑yield die; packaging recipes with In bumps and fine‑pitch LGA laminates.

- Dependencies/assumptions: Supply of isotopically enriched materials; integration of Nb and W metallization in CMOS facilities; consistent valley engineering; ESD/magnetic hygiene practices.

- Quantum hardware test & metrology: “cryoMUX” noise characterization to separate intrinsic vs extrinsic errors

- Use: Quantify charge noise (N_osc) and magnetic noise (T2*) in situ to attribute performance limits and prioritize fixes (e.g., contextual miscalibration, static gradients).

- Tools/products/workflows: Cryogenic demultiplexer modules controlling 9‑dot subsets; standardized noise parametrics reported alongside gate errors.

- Dependencies/assumptions: RT electronics integration; calibration fits to map noise metrics to gate error budgets; stable zero‑field operation.

- Quantum hardware design & operations: Zero‑field operation with permutational dynamical decoupling

- Use: Run at near‑zero magnetic field with vector cancellation coils to suppress superconductivity‑induced gradients; apply NZ1 decoupling to stabilize idling qubits during dense schedules.

- Tools/products/workflows: Magnetic hygiene toolkit (vector coils + software); schedule templates applying NZ1 during SPAM, two‑qubit, and leakage‑reduction windows.

- Dependencies/assumptions: Adequate coil access and calibration; compatibility with device materials (avoid flux trapping); sequencing support in controller ISA.

- Quantum control software: Compiler and instruction‑set for time‑modulated, gate‑synchronized switching

- Use: Convert high‑level qubit programs into instruction streams that drive parallel sequencers and pattern memories, enabling fast, shape‑insensitive EO pulses.

- Tools/products/workflows: ISA documentation; codegen libraries; memory‑efficient randomized benchmarking leveraging on‑chip PRNGs.

- Dependencies/assumptions: Stable firmware; predictable timing closure between digital and analog layers; sufficient instruction memory (6,144 words) for target experiments.

- Test & measurement vendors/Cryo readout: 4 K transimpedance amplifiers (TIAs) for charge sensing

- Use: Integrate low‑capacitance, 4 K TIAs positioned near mK boards to improve sensor bandwidth and SNR in quantum dot readout.

- Tools/products/workflows: Modular TIA units with thermal anchoring at 4 K; reference designs for integration with dilution fridges.

- Dependencies/assumptions: Thermal/mechanical accommodation; noise performance under magnetic mitigation; cabling parasitics compatible with ~3 ns round‑trip lengths.

- Policy & standards: Reference metrics and test protocols for “well‑behaved” errors in small QPUs

- Use: Promote reporting of LER, DEF, DEM results, and gate error distributions as procurement/benchmark standards for funded testbeds.

- Tools/products/workflows: Program calls that require standardized QEC‑readiness tests (e.g., repetition code scaling factors, [[4,2,2]] post‑selection fidelity).

- Dependencies/assumptions: Community agreement on protocol details; shared tools for DEM analysis.

- Education/Workforce: EO‑qubit control and QEC labs

- Use: Course modules demonstrating exchange‑only control, dynamical decoupling, and leakage management with small qubit arrays.

- Tools/products/workflows: Simulators (spin‑ and event‑level); open data sets for repetition/[[4,2,2]] experiments; lab kits using the control architecture in emulation.

- Dependencies/assumptions: Access to emulation or small cryo testbeds; safety and training for cryogenic systems.

Long‑Term Applications

Translating the paper’s prototype into utility‑scale systems and broader markets requires further research, scaling, and product maturation:

- Cloud/High‑performance computing; Software & pharma/materials: Utility‑scale, fault‑tolerant silicon spin‑qubit quantum computers in a single commercial cryostat

- Use: Run error‑corrected algorithms for chemistry, materials, optimization, and machine learning with manageable capital and operational costs.

- Tools/products/workflows: Large EO qubit arrays with nearest‑neighbor connectivity; integrated cryo‑control ASICs with sub‑mW/qubit power; in‑cryostat digitization (cryo‑ADCs) and decoding; system‑level architectures tailored to EO noise and connectivity.

- Dependencies/assumptions: Further reduction of extrinsic errors (magnetic hygiene, signal integrity, calibration automation), improved device uniformity and yield, scalable interconnect/back‑end routing, robust decoders, and verified thresholds at scale.

- Semiconductor & cryo‑electronics industry: Product family of cryo‑CMOS controllers and cryo‑ADCs

- Use: Commodity 4 K control/digitization chips for multiple quantum modalities (spin qubits, superconducting circuits, sensor arrays).

- Tools/products/workflows: Low‑power controllers with higher channel density; 1 GS/s cryo‑SAR ADCs integrated near mK; standardized digital buses and firmware.

- Dependencies/assumptions: Mature cryo transistor models and PDKs; long‑term reliability data at 4 K; foundry and packaging supply chains for cryo operation.

- Cryogenic interconnect market: Standardized high‑density superconducting backplanes

- Use: Interoperable ribbon/backplane standards connecting 4 K electronics to mK modules across vendors.

- Tools/products/workflows: Connector standards, mechanical form factors, EMI shield specs; DfM guidelines for Nb‑on‑polyimide.

- Dependencies/assumptions: Industry consortia; qualification across thermal cycles and vibrations; cost‑effective wafer‑level fabrication.

- Quantum sensors & space/aerospace instrumentation: Low‑thermal‑load, high‑bandwidth wiring for large cryo detector arrays

- Use: Scale TES/MKID/SQUID arrays in astrophysics and remote sensing with minimal heat load to mK and improved bandwidth.

- Tools/products/workflows: Adapted ribbon assemblies and 4 K control/readout ICs; multiplexed readout schemes integrated on cable/boards.

- Dependencies/assumptions: Sensor‑specific EMC requirements; radiation tolerance for space; long‑term cryo reliability.

- System architecture & software stack: EO‑specific QEC and scheduling frameworks

- Use: Compilers, schedulers, and decoders co‑designed with EO constraints (nearest‑neighbor, exchange‑only, leakage channels, NZ1 idling).

- Tools/products/workflows: Context‑aware calibration and model‑based control to suppress coherent/contextual miscalibrations; scalable DEM‑driven health monitoring.

- Dependencies/assumptions: Stable device models exhibiting “emergent Markovianity”; continuous integration of hardware telemetry into calibration loops.

- Energy & facilities: Cryo‑data‑center modules optimized for 4 K control + mK compute

- Use: Modular cryostats hosting QPUs with defined thermal budgets, power delivery, and serviceability.

- Tools/products/workflows: Facility design kits (FDKs) specifying power, cooling, vibration, and magnetic shielding; TCO models (W/qubit, kWh per logical qubit‑cycle).

- Dependencies/assumptions: Reliable cryocoolers; standardized maintenance interfaces; regulatory guidance for helium use and cryogen safety.

- Standards & policy: Interoperability and benchmarking frameworks for cryogenic quantum systems

- Use: Define minimum reporting (gate errors, LER scaling, DEM), interconnect pinouts, and safety/EMC standards for cryogenic electronics.

- Tools/products/workflows: Joint working groups (industry/academia/government); conformity tests for procurement and grants.

- Dependencies/assumptions: Broad stakeholder participation; harmonization with international standards bodies.

- Education & workforce (advanced): Training pipelines for cryo‑CMOS, quantum device fabrication, and systems integration

- Use: Specialized curricula and apprenticeships to build the workforce required for scaled manufacturing and operation.

- Tools/products/workflows: University–industry programs; shared testbeds and design challenges (e.g., controller power‑per‑qubit reductions).

- Dependencies/assumptions: Sustained funding; access to cryo facilities and enriched materials.

- Cross‑modality translation: Applying NZ1 permutational decoupling and leakage‑aware gadgets to other encoded qubits

- Use: Adapt EO‑style decoupling and reset‑if‑leaked sequences to other multi‑spin or encoded qubit systems where leakage and low‑field operation are relevant.

- Tools/products/workflows: Theoretical mappings; firmware libraries for alternate modalities.

- Dependencies/assumptions: Physical compatibility with exchange‑like or SWAP‑like operations; validated error models.

- Quality & reliability engineering: Predictive, local‑to‑system performance qualification

- Use: Use local parametrics (gate errors, N_osc, T2*) and DEM to predict system‑level performance for acceptance and binning.

- Tools/products/workflows: Statistical QA pipelines; vendor/customer SLAs based on standardized metrics.

- Dependencies/assumptions: Stable correlations between local metrics and logical performance across lots and revisions.

Notes on feasibility: Immediate adoption hinges on access to the described hardware (cryo‑CMOS controller, ribbon cable, device process) and on integrating magnetic hygiene, calibration, and readout. Long‑term deployment requires power‑per‑qubit reductions, manufacturable interconnect/back‑end routing at scale, improved device uniformity/yield, and end‑to‑end software–hardware co‑design for error correction.

Glossary

- Ancilla: A helper qubit used to extract syndromes or assist operations without storing logical information. "using two ancilla qubits."

- baseband: Low-frequency (near-DC) control signaling without RF carriers. "direct-current (DC) or ``baseband'' pulsing"

- blind randomized benchmarking (BRB): A benchmarking protocol that hides certain sequence details to estimate gate errors and leakage. "are characterized with blind randomized benchmarking (BRB)"

- Carnot efficiency: The theoretical maximum efficiency of a heat engine, relevant for cryogenic cooling tradeoffs. "This third option enjoys greater Carnot efficiency"

- charge noise: Fluctuations in electric potential that perturb qubit energies and couplings. "The intrinsic charge noise of these devices is more than an order of magnitude lower"

- co-planar waveguide stack: A layered transmission-line structure used for high-frequency on-chip routing. "formed in a co-planar waveguide stack"

- CNOT: A controlled-NOT two-qubit gate used for entangling operations. "CNOT sequences..., composed of 37 pulses in 45 timesteps, are characterized with an interleaved BRB variant"

- cryoMUX system: A cryogenic multiplexing system for selecting and controlling subsets of device dots. "using a purpose-designed ``cryoMUX'' system."

- cryogenic CMOS controller: A complementary-metal–oxide–semiconductor control chip designed to operate at cryogenic temperatures. "The cryogenic CMOS controller."

- decoherence free subsystem: An encoding that protects quantum information against certain collective noise by symmetry. "using the symmetry-respecting encoding of a decoherence free subsystem"

- detector event fraction (DEF): The fraction of syndrome rounds where a detection event (error indication) occurs. "leads to a stable detector event fraction (DEF)"

- detector-error-model (DEM) analysis: A method that models which error patterns explain observed detector outcomes. "we turn to detector-error-model (DEM) analysis"

- dilution refrigerator: An ultra-low-temperature cryostat reaching millikelvin temperatures for quantum devices. "Devices are installed on a daughterboard thermalized to the mixing chamber of a dilution refrigerator."

- Empirical cumulative distribution functions (ECDF): A nonparametric statistic showing the distribution of observed values up to a given threshold. "Empirical cumulative distribution functions (ECDF) for gate error"

- exchange interaction: A spin–spin interaction arising from wavefunction overlap and the Pauli principle, used to implement gates. "The resulting ``exchange interaction'' reduces the energy of the singlet state relative to all triplet states"

- exchange-only (EO) qubits: Spin qubits manipulated solely by exchange interactions, avoiding local magnetic fields. "Silicon exchange-only (EO) qubits"

- exchangles: Exchange rotation angles determined by the time-integral of exchange energy. "which we call exchange angles or ``exchangles''"

- exchange pulses: Voltage pulses that modulate exchange coupling to enact spin-swap operations. "Single-qubit gates, each composed of 4 exchange pulses"

- flag qubit: A qubit measured to signal the presence of certain fault patterns during syndrome extraction. "interleaved flag qubit measurements"

- full-permutation dynamical decoupling: A decoupling sequence that permutes spins to average out local noise. "first-order ``NZ1'' full-permutation dynamical decoupling"

- gate driver: Analog circuitry that delivers shaped voltages to device gates for qubit control. "The gate driver layer is composed of an array of 78 nearly-identical analog blocks"

- instruction set architecture: The defined command set the controller executes to orchestrate qubit operations. "uses a custom instruction set architecture for qubit control."

- interleaved BRB: A BRB variant where target gates are interleaved to isolate their error. "are characterized with an interleaved BRB variant"

- isotopically enhanced: Enrichment of isotopes (e.g., 28Si) to reduce nuclear-spin noise. "Si and Ge in the heterostructure are isotopically enhanced to reduce magnetic noise."

- land grid array (LGA) package: A chip package with an array of contacts on the underside for board attachment. "bump bonded to a fine-pitch laminate LGA package"

- leakage reduction units (LRUs): Control sequences that identify and reset qubits that have leaked out of the computational subspace. "The leakage reduction units (LRUs) used here"

- logical error rate (LER): The probability that a logical qubit experiences an error per round or cycle. "indicate a logical error rate (LER) of 5.0 for the distance 5 code"

- Markovianity: The property that errors have no memory beyond the current step (lack temporal correlations). "an encouraging indication that our system exhibits emergent Markovianity"

- mixing chamber: The coldest stage of a dilution refrigerator where devices are mounted. "thermalized to the mixing chamber of a dilution refrigerator."

- near-end crosstalk: Unwanted coupling between adjacent lines measured near the signal source. "near-end crosstalk up to 10 GHz is limited to ~dB."

- NZ1: A specific first-order dynamical decoupling sequence variant used in permutation-based decoupling. "first-order ``NZ1'' full-permutation dynamical decoupling"

- Pauli-exclusion principle: The quantum rule prohibiting identical fermions from occupying the same state, underlying exchange interactions. "Pauli-exclusion principle."

- Pauli-spin blockade: A transport blockade used for spin readout/initialization based on spin selection rules. "Pauli-spin blockade mechanism"

- pattern memory: On-chip memory that stores voltage and timing patterns for analog outputs. "Pattern memory associated with each output stores parameters for voltages and pulse widths."

- permutational dynamical decoupling: A technique that averages local noise by permuting spins with SWAP operations. "using permutational dynamical decoupling."

- pseudo-random number generators: On-chip generators used for stochastic sequences without large memory footprints. "On-chip pseudo-random number generators enable memory-efficient characterization of qubit performance."

- quantum dots: Nanoscale potential wells confining single electrons to implement spin qubits. "54 exchange-coupled quantum dots"

- quantum error correction (QEC): Techniques that encode and protect quantum information against errors. "the overhead required for quantum error correction (QEC)."

- quantum error detecting (QED) code: A code that detects (but may not correct) certain error patterns via stabilizer measurements. "a quantum error detecting (QED) code"

- quantum processing unit (QPU): An integrated module combining qubits, control, and interconnect as a quantum compute element. "this ``quantum processing unit'' (QPU"

- repetition code: A code that redundantly encodes classical information to detect and suppress bit/phase flips. "a distance-5 repetition code"

- Reset-If-Leaked (RIL): A control sequence that resets a qubit only if it has leaked from the logical subspace. "a Reset-If-Leaked (RIL) control sequence"

- Serial Peripheral Interface (SPI): A synchronous serial bus used here for configuration and readback. "a Serial Peripheral Interface (SPI) for configuration, diagnostics, and memory readback."

- Si/SiGe quantum well: A silicon quantum well in a silicon–germanium heterostructure used to confine electrons. "Electrons are vertically confined in a Si/SiGe quantum well"

- superconducting ribbon cable: A flexible, low-thermal-conductance, high-density interconnect for cryogenic signals. "A high-density superconducting ribbon cable routes signals from the controller to the qubit chip."

- symmetric exchange operation: A gate scheme that drives exchange symmetrically across neighboring gates to reduce sensitivity to errors. "To actuate symmetric exchange operation"

- syndrome extraction (SE): The process of measuring stabilizers to detect errors in an error-correcting code. "Each syndrome extraction (SE) round is broken into two waves"

- T2* (dephasing time): The inhomogeneous dephasing time characterizing decay of coherent oscillations due to quasi-static noise. "singlet decay experiment, "

- thermal standoff: A structure that provides electrical connection while impeding heat flow between temperature stages. "also serving as a thermal standoff"

- transimpedance amplifier (TIA): An amplifier that converts input current to a proportional output voltage. "transimpedance amplifiers (TIAs"

- valley splitting: The energy separation between conduction-band valleys in silicon, crucial for spin qubit performance. "engineered to increase valley splitting."

- weight-4 measurements: Stabilizer checks acting on four qubits simultaneously (e.g., XXXX, ZZZZ). "two weight-4 measurements ( and )"

- wiring bottleneck: The scalability limit imposed by the number and quality of room-temperature-to-cryostat cables. "the room temperature ``wiring bottleneck,''"

Collections

Sign up for free to add this paper to one or more collections.