- The paper presents a systems-level engineering roadmap to scale superconducting quantum processors for FTQEC, emphasizing modular architectures from chip packages to inter-cryostat links.

- It analyzes the challenges of cryogenic systems and control electronics, proposing advanced cryogenic cabling, modular fridges, and integration of cryoCMOS for energy-efficient scaling.

- It recommends standardized testbeds, reliability protocols, and high-threshold qLDPC codes to overcome scalability bottlenecks and enable real-time error correction.

Enabling Technologies for Scalable Superconducting Quantum Computing

Introduction and Context

The paper "Enabling Technologies for Scalable Superconducting Quantum Computing" (2512.15001) provides an exhaustive technological roadmap for the systems-level engineering required to scale superconducting quantum processors to the regime needed for large-scale fault-tolerant quantum error correction (FTQEC). Rather than focusing simply on qubit coherence improvements or quantum device materials, the report systematically addresses the entire stack from modular quantum processor unit (QPU) design through to cryogenic infrastructure, classical control systems, interconnects, error correction architectures, and scalable benchmarking.

Modular Architectures for Quantum Processors

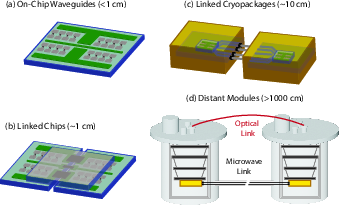

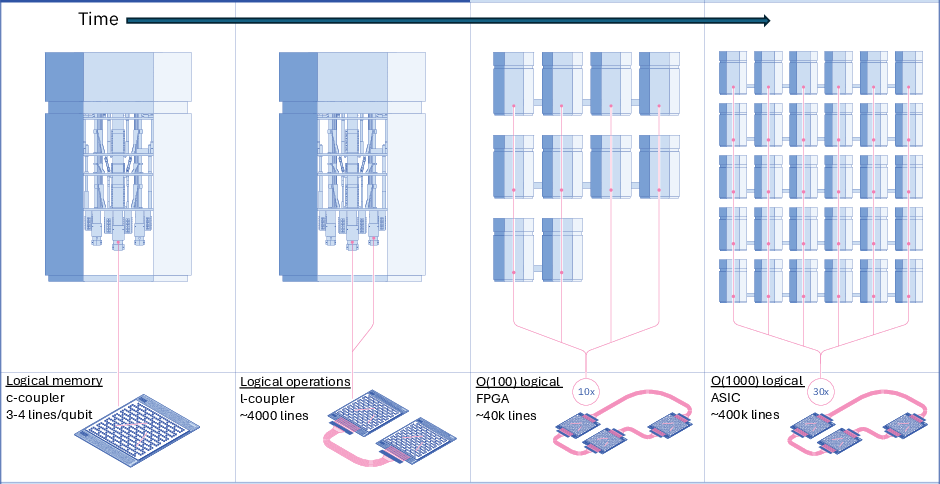

Scaling qubit numbers on a single substrate is increasingly limited by yield, frequency collisions, and control/readout wiring complexity. The paper advocates for modular approaches—ranging from multi-chip assemblies on a shared substrate, through independent chip packages connected by cryogenic cabling, to fully decoupled modules linked by either microwave or optical photon communication.

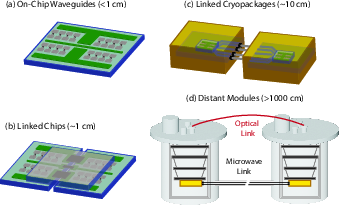

Figure 1: Modular QPU architectures showing various interconnect strategies from on-chip microwave lines to optical links between cryostats.

A hierarchical modularity is outlined:

- Direct galvanic coupling at short ranges (on-chip lines or close modules)

- Cryogenic microwave cabling for medium-range (centimeter–meter scale) interconnects, leveraging recent advances in ultralow-loss Al cables (below 0.4 dB/km at 20 mK [QIU2024, niu_low-loss_2023])

- For longer distances or inter-cryostat scaling (beyond ~1 m), quantum microwave–optical transduction is required, the latter relying on high-cooperativity electro-optic, piezo-optomechanical, or atomic transducer technologies [meesala_quantum_2024, fan_superconducting_2018, xu_bidirectional_2021, sahu_quantum-enabled_2022, weaver_integrated_2024].

While modularity offers improvements in manufacturability and flexibility, it introduces nontrivial code deformation and cross-module error correction requirements, with separation of modules significantly impacting code distance and logical error rates. The deployment of high-threshold, hardware-efficient qLDPC codes [bravyi_high-threshold_2023] and modular code architectures [yoder2025tourgrossmodularquantum] is therefore posited as essential.

Cryogenic Systems and Energy Efficiency

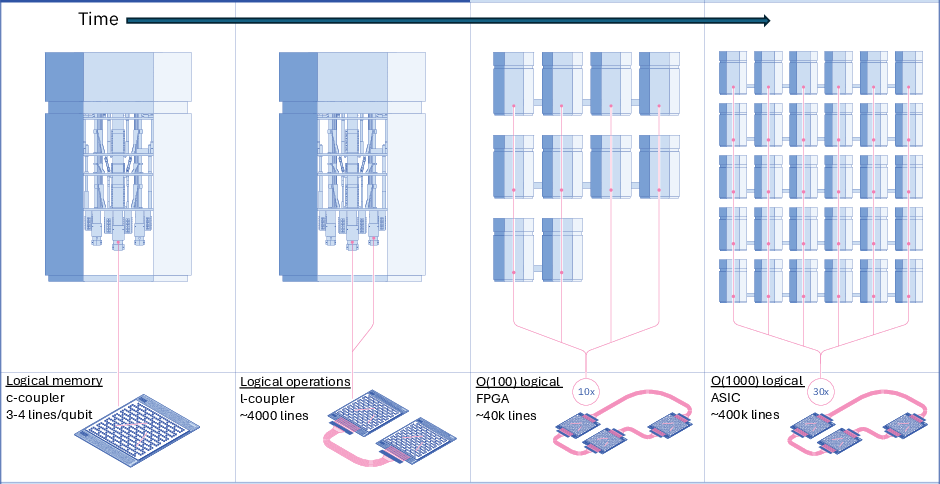

Cryogenic systems remain a dominant scaling and cost bottleneck. Even "large" dilution refrigerators support only 20–30 μW at 20 mK, with total module wall power exceeding 10 kW, and future wall power requirements for FTQEC-scale machines projected to approach or surpass those of classical data centers. Extensibility via modular cryogenic units—each supporting ~1000 qubits, interconnected both thermally and via signal links—is recommended as the only path to data-center-scale quantum systems.

Figure 2: Schematic of fridge extensibility, showing modular dilution fridges linked to create a contiguous quantum network and payload volume.

A critical resourcing issue is the long-term supply and cost of 3He, a rare isotope essential for dilution cooling at scale; super-linear demand growth could induce global supply crises without advances in alternative refrigeration strategies or drastic reductions in per-qubit 3He utilization.

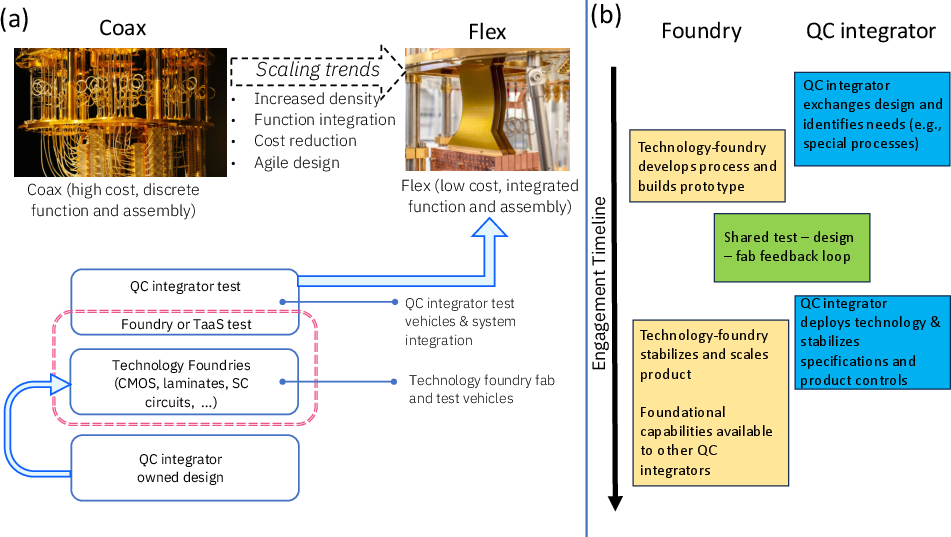

Cryogenic and Classical Electronics, Integration, and Foundry Model

The signal I/O and control electronics stack is called out as a central impediment to scaling. Direct analog wiring scales poorly in terms of space, thermal load, and cost. Multiple approaches to mitigation are discussed:

This systems engineering is underpinned by a strong assertion: the lack of standardized, high-throughput, cryogenic testing as a service is currently stalling ecosystem growth.

Control Hardware, Error Correction, and Algorithmic Stack

The control electronics system, both at room and cryogenic temperatures, must:

- Provide high-density, programmable RF/flux drive and readout for each channel

- Enable low-latency error syndrome extraction and decoding for real-time QEC feedback

- Maintain low cost (<$100s per qubit) at the 105+ qubit scale via ASIC/SoC solutions, as outlined in recent industrial roadmaps [ZettlesWJWA22, ParkIntel21]

The authors also emphasize a sharply increased need for robust reliability analysis of cryoelectronic components, given the time/cost overheads caused by cooling cycles for replacement, and the critical role of real-time error correction protocols.

Quantum error correction is explored in detail, with the classical minimum-weight perfect matching (MWPM) decoder's suitability called into question for new modular architectures, high-rate qLDPC codes, and correlated error environments. The need for decoders capable of exploiting learned noise models [Iyer2025, iyer2025enhancing], accommodating heterogeneous link fidelities and topological defects, and balancing latency with accuracy is expressed as a major open problem.

QPU Operation, Calibration, and Benchmarking

As QPU sizes grow, the overhead of comprehensive pulse calibration and error benchmarking increases superlinearly. The report enumerates scalable strategies:

- Hierarchical calibration routines and shortcut learning methods under simplified noise models, validated by global cycle benchmarking [erhard2019characterizing, EPLG, Hashim_2025]

- Resource-efficient randomized compiling [wallman2016noise, hashim_randomized_2020], which stochastizes coherent errors and aligns logical error models with those assumed in theoretical codes

- Emphasis on efficient Pauli error learning [Emerson2007, carignan2024estimating, chen2023learnability] and scalable output validation metrics, such as total variation distance estimation via circuit benchmarking [QCAP]

Robust classical compute support for decoder operations, error-mitigation post-processing, and calibration feedback is highlighted as essential and may drive the implementation of heterogeneous, tightly integrated quantum-classical compute systems in large-scale deployments.

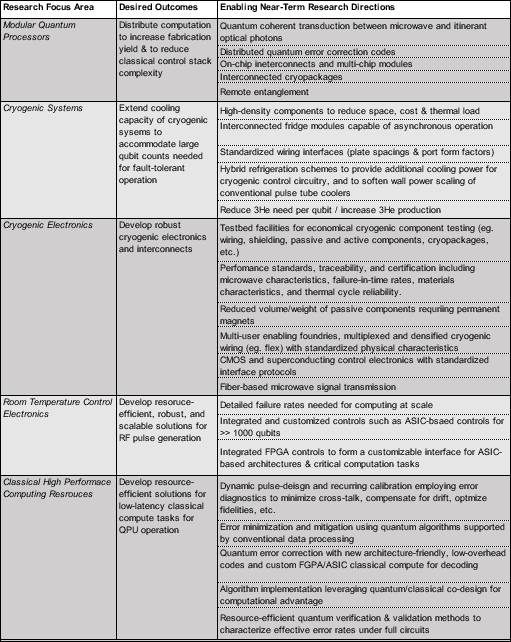

Selected Major Recommendations

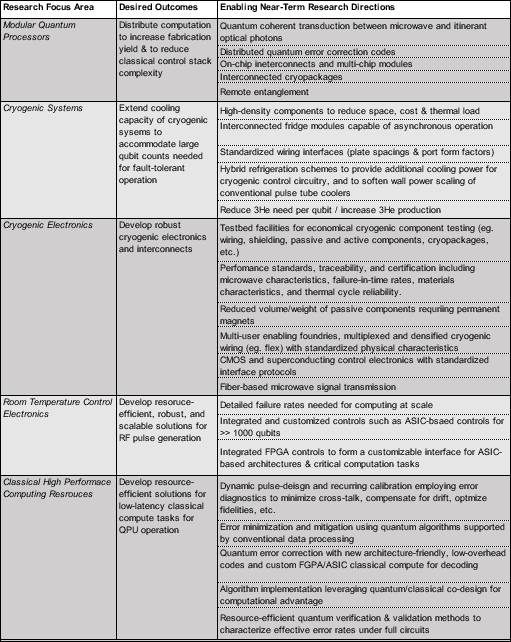

Figure 4: Consolidated major recommendations addressing modularity, extensibility, electronics/test infrastructure, QEC, benchmarking, and output validation.

The report's strong claims and recommendations include:

- Exclusive reliance on monolithic increases in fridge size is nonviable—modular, extensible architectures are a necessity.

- Lack of standardized component testing, qualification, and reliability analysis is an ecosystem bottleneck.

- Adoption of high-threshold, hardware-efficient qLDPC codes is no longer optional for scalable architectures.

- Cryogenic control electronics must be treated as a distinct reliability and cost optimization problem, not simply an extension of room-temperature approaches.

- Resource- and latency-constrained real-time error correction, diagnosis, and decoding is a central systems challenge that will dominate practical FTQEC deployments.

Future Directions and Implications

Realizing practical FTQEC systems based on superconducting circuits requires both foundational and systems-engineering advances. On the fundamental side, scalable quantum transducers for microwave-optical interfacing will be critical for distributed quantum computing and quantum networking applications [meesala_quantum_2024, ang_arquin_2024]. On the systems side, vertical integration of component supply chains, modular testbeds, and standardized design-qualification workflows will become increasingly necessary, especially as qubit numbers scale and application requirements mature.

Practically, the paper projects that the cost, energy usage, space, and error correction stack of future superconducting QPU data centers will increasingly resemble those of modern high-performance computing facilities, albeit with significant new constraints in thermodynamics, physical integration, and supply chain management (notably 3He sourcing).

On the theoretical side, these system-level advances will make possible the implementation and exploration of large logical qubit architectures: quantum algorithms for chemistry, optimization, and machine learning at scales beyond classical reach appear increasingly feasible, provided these supporting technological bridges are built.

Conclusion

This paper systematically analyzes the technical and ecosystem challenges to scaling superconducting quantum computing from current small- and intermediate-scale demonstrations to the large-scale, error-corrected regime capable of delivering practical quantum advantage. It emphasizes that success requires coordinated advances in modular QPU architectures, cryogenic extensibility, miniaturized and standardized control electronics, robust test and qualification infrastructure, high-rate and hardware-efficient error-correcting codes, low-latency syndrome decoding, and resource-efficient benchmarking. Continuing progress in these enabling technologies is foundational for the emergence of practical FTQEC, with broad implications spanning both the physical engineering of quantum hardware and the future role of quantum computing in computational science.