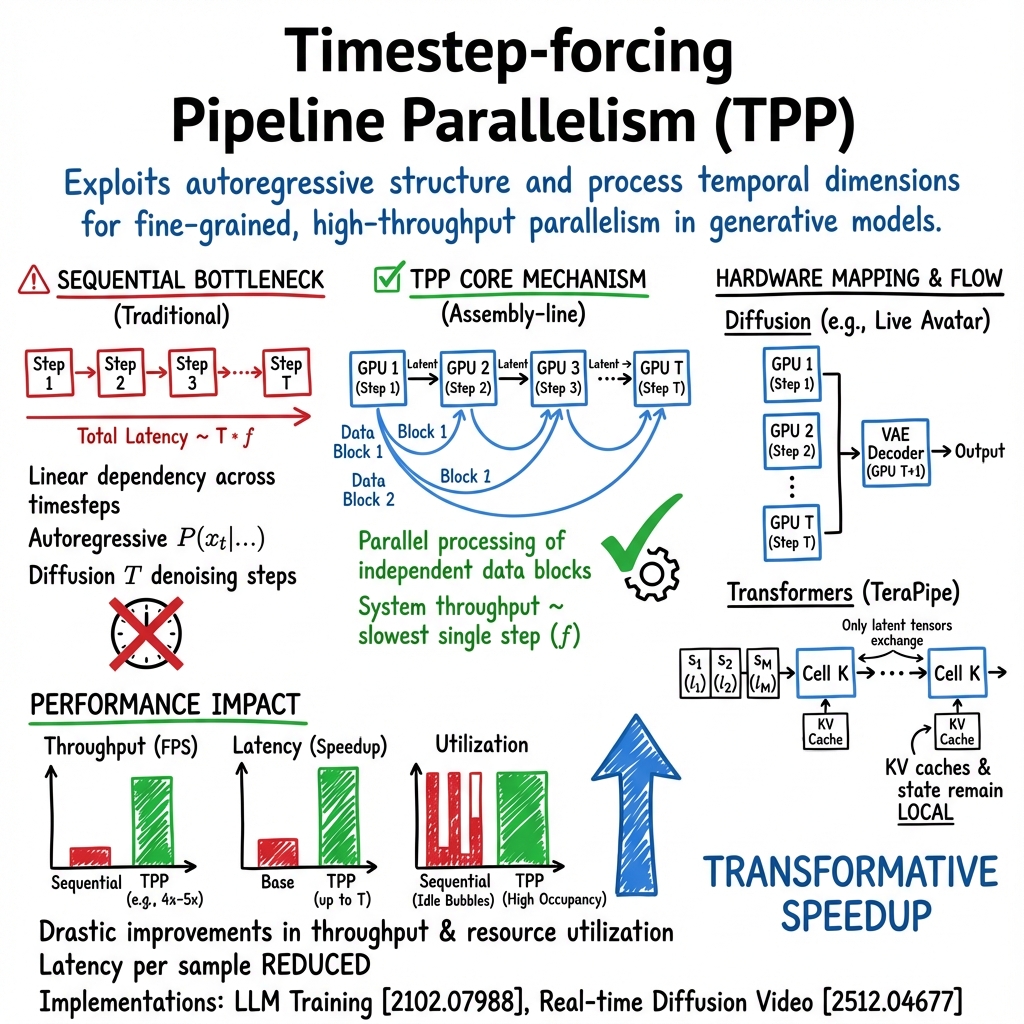

Timestep-Forcing Pipeline Parallelism (TPP)

- TPP is a distributed computation paradigm that leverages autoregressive temporal dependencies by assigning each timestep or token slice to dedicated processing units for fine-grained parallel execution.

- It partitions large-scale generative models across GPUs by mapping discrete timesteps, which reduces iteration latency and maximizes throughput in both training and inference.

- TPP overcomes bottlenecks of traditional pipeline and data parallelism, though its optimal performance requires a rigid one-to-one device-to-timestep mapping and incurs a high memory footprint.

Timestep-forcing Pipeline Parallelism (TPP) is a distributed computation paradigm that exploits the autoregressive structure and process temporal dimensions of large-scale generative models to achieve fine-grained, high-throughput parallelism. TPP diverges from traditional pipeline parallelism, which partitions models by depth (layers) and relies on micro-batch pipelining. Instead, TPP assigns distinct timesteps or token slices—mapped to discrete generative or denoising stages—across multiple processing units, enabling synchronous execution along the time axis. This architectural innovation has enabled both LLM training (Li et al., 2021) and real-time diffusion-based video synthesis (Huang et al., 4 Dec 2025), demonstrating transformative reductions in iteration latency and drastic improvements in throughput.

1. Motivation and Computational Bottlenecks

TPP emerged from the need to address two fundamental bottlenecks in large-scale autoregressive and diffusion model pipelines: the sequential dependency across timesteps in generative inference and training, and the inefficiency of classical layer-based pipeline parallelism under long-horizon, temporally causal computation.

In autoregressive Transformers, the factorization enforces strict left-to-right token-by-token processing. Likewise, DDPM-style video diffusion models require each sample to propagate sequentially through denoising steps, with each step dependent on the previous latent state. The result is a "time-chain" bottleneck, where the total latency per data sample grows linearly with the number of steps, and parallel strategies operating solely on the data or batch dimension (data parallelism) cannot accelerate per-sample completion.

TPP breaks this bottleneck by converting the sequence of dependent steps into a hardware-level depth pipeline: each device manages a discrete timestep (for Diffusion) or token slice (for Transformers), allowing simultaneous processing of independent data blocks. This enables an assembly-line paradigm in which system throughput is determined by the slowest single step rather than the full sequence, dramatically improving resource utilization.

2. Architectural Principles and Hardware Mapping

TPP partitions computational work by aligning model timesteps or token slices to hardware resources. For diffusion-based video synthesis ("Live Avatar" (Huang et al., 4 Dec 2025)), the backbone is mapped as follows:

- GPUs for the diffusion backbone, with each GPU dedicated to a single denoising step.

- An additional GPU for VAE decoding, completing the inference trajectory from latent to RGB frames.

Each data block (e.g., a video chunk of frames) enters the first GPU as initial noise, then cascades through sequential timesteps—each managed and executed exclusively by a dedicated GPU. This mapping maximizes parallel occupancy once the pipeline is filled, resulting in throughput of approximately $1/f$ (where is the single-step forward time) instead of for sequential execution.

For Transformer training ("TeraPipe" (Li et al., 2021)), token-level parallelism is achieved by dividing a sequence of length into slices: each slice of length enters the pipeline, where model layers are partitioned into contiguous "cells." As each cell finishes processing a token, the next cell begins, creating a temporal wavefront along the architecture.

Both implementations require point-to-point high-bandwidth interconnects (e.g., NVLink), with per-step communication limited to latent tensors; no layer activations or transformer KV caches traverse device boundaries.

3. Algorithmic Schemes and Execution Wavefronts

The core algorithm in TPP for diffusion inference is a depth-wise pipeline where each GPU executes:

- Receives input latent (or samples initial noise for the first step).

- Executes the denoising function for its assigned step.

- Updates the latent using Euler or other integration ().

- Locally manages and updates transformer KV caches, restricted to rolling windows for causal consistency.

- Forwards the updated latent to the next GPU in the pipeline.

A pseudocode representative of the process (from (Huang et al., 4 Dec 2025)):

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

for each block i=1..M do if k == 1: x ← Normal(0, I) else: x ← recv(from GPU k−1) if k ≤ T: v_hat, kv_new ← DiT_k(x; t_{T−k+1}, KV_cache, cond, sink_frame) x ← x + v_hat × Δt KV_cache.append(kv_new) if KV_cache.size > w: pop_front(KV_cache) send(x, to GPU k+1) else: rgb_block ← VAE(x) output(rgb_block) end |

For Transformer models, the pipelining strategy is governed by dynamic programming. Slices are selected to minimize total pipeline latency , subject to hardware and comm/compute constraints, with per-slice costs empirically fit.

Both architectures incorporate a warm-up stage: initial data blocks cascade through the pipeline sequentially, after which steady-state is reached and all GPUs work concurrently.

4. Communication, Synchronization, and Data Locality

TPP is characterized by strict local synchronization and minimal communication:

- Only the latent tensor representing the current block transits across GPU boundaries at each timestep.

- Transformer KV caches and auxiliary states remain strictly local to each device and are managed independently, eliminating cross-GPU dependency and reducing bandwidth requirements.

- No global collective or all-reduce operations are required; handoffs follow a lock-step receive-compute-send cycle.

- Occasional broadcast events (e.g., "sink frame" updates in streaming avatars) are infrequent and do not perturb the steady-state throughput.

Warm-up ensures orderly filling of the pipeline, after which deterministic operation proceeds without idle bubbles. The fill-drain penalty is at the start but negligible over long streams.

5. Performance Analysis and Scaling

Empirical and theoretical speedup is central to TPP's impact. Sequential latency per block is . Pipeline parallel throughput reaches , with speedup if . Demonstrated benchmarks include:

| Model (Params) | Steps (T) | Pipeline GPUs | Sequential FPS | TPP FPS | Speedup |

|---|---|---|---|---|---|

| DiT-14B (Live Avatar) (Huang et al., 4 Dec 2025) | 4 | 4+1 VAE | ~5 | 20.88 | 4× |

| GPT-3-175B (TeraPipe) (Li et al., 2021) | – | 48 | – | – | 5× |

| GPT-3-44B (TeraPipe) | – | – | – | – | 2.4× |

Longer sequences () and more timesteps () exacerbate the speedup, as fill-drain penalties become increasingly negligible. TTFF (time-to-first-frame) is unchanged, remaining at since initial blocks traverse the full pipeline before output.

Dynamic programming optimizers for token slicing further reduce latency over uniform schemes, yielding up to 1.12× additional speedup for Transformers.

6. Comparison with Baseline Parallelization Schemes

TPP departs from both model-split pipeline parallelism (GPipe, Torch-Pipe) and standard data parallelism:

- Model-split PP partitions by layers; micro-batch pipelining overlaps different batches on pipeline stages, but fails to break sequential time dependencies. Each sample still undergoes all or steps in series.

- Data parallelism replicates entire models across GPUs, improving batch throughput but not individual sample latency. Per-block completion remains bound by sequential step execution.

TPP alone allows throughput acceleration for streaming and real-time applications with large models (DiT 14B at 20 FPS), a regime previously unattainable.

| Parallelism Type | Partition Axis | Reduces Latency per Sample | Reduces Throughput per Batch |

|---|---|---|---|

| Data Parallel | Batch | No | Yes |

| Model-Split PP | Layers | No | Yes (micro-batch) |

| TPP | Time/Token | Yes | Yes |

A plausible implication is that future large-scale models requiring strict temporal or causal computation will increasingly adopt TPP-based strategies for both training and inference.

7. Strengths, Limitations, and Implementation Considerations

Strengths of TPP include:

- Deterministic, robust, and high-throughput operation after pipeline warm-up.

- Orders-of-magnitude reduction in idle time; steady-state GPU utilization at peak.

- Minimal inter-device communication; only requisite latent tensors are exchanged.

- Extensibility: step-to-GPU mapping scales with the number of compressed timesteps; reduction in model depth or step count immediately translates to hardware scaling.

Limitations remain:

- TTFF reduction is unattainable; first output is bounded by traversal of all sequential steps.

- Step-to-GPU ratio is rigid: optimal mapping requires devices. Fewer GPUs necessitate grouping, limiting speedup.

- Memory footprint per GPU is large; each device holds a full model copy and local state, restricting applicability for models far exceeding 14B parameters.

TPP architectures have demonstrated real-time, high-fidelity streaming at industrial scale (20 FPS at 14B parameters) (Huang et al., 4 Dec 2025), as well as transformative wall-clock speedups for Transformer training at massive scales (Li et al., 2021). This paradigm is foundational for subsequent advances in temporal and causal model deployment in both academic and applied contexts.