Gated Delta Rule in Neural Networks

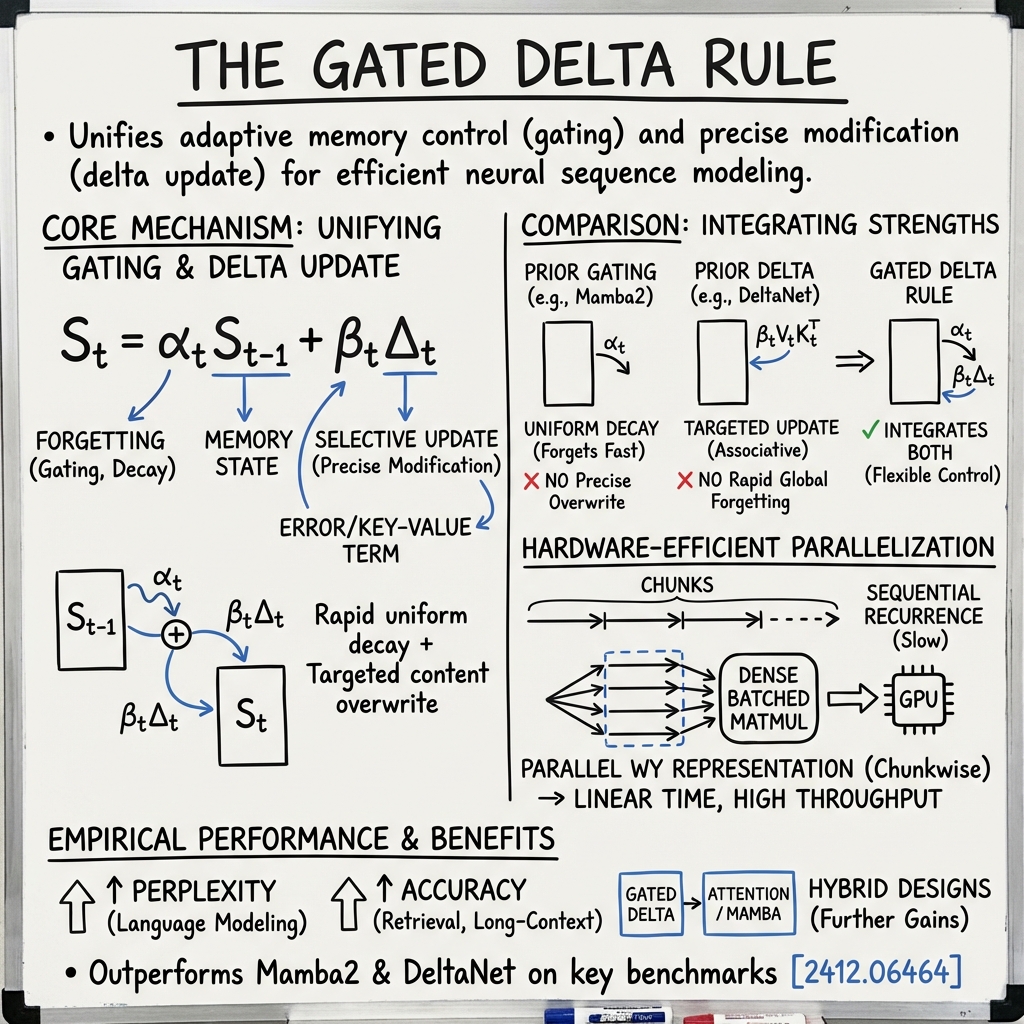

- Gated Delta Rule is a mechanism that unifies adaptive memory gating with delta-style updates, combining rapid forgetting and precise memory modification.

- It employs explicit data-dependent gating factors (α and β) to enable uniform decay and selective updates, overcoming limitations of traditional delta rules.

- Hardware-efficient chunkwise parallelization and WY representation allow scalable training and improved performance on language modeling and long-context tasks.

The gated delta rule refers to a mechanism developed to unify adaptive memory control (gating) and precise memory modification (delta update) in recurrent neural architectures, especially linear recurrent networks and transformers. It enables both rapid, uniform forgetting of outdated information and selective updating of salient content. This approach is distinct from prior delta rule formulations (e.g., classic Widrow–Hoff, DeltaNet), introducing explicit gates and leveraging a parallel hardware-efficient implementation. Recent work demonstrates that gated delta rule–based architectures such as Gated DeltaNet surpass models like Mamba2 and DeltaNet on multiple language modeling, retrieval, and long-context benchmarks (Yang et al., 2024).

1. Mathematical Formulation of the Gated Delta Rule

At each timestep , the gated delta rule prescribes the state update: where:

- is the previous state (memory).

- is a data-dependent gating factor allowing rapid uniform decay or forgetting.

- is a learned delta-update rate controlling the contribution of the targeted update.

- is an error-like term constructed from the current input, typically involving key–value associations.

In Gated DeltaNet (Yang et al., 2024), the delta update adopts an outer-product form, frequently realized as: where is the current value vector and accumulates gating over time. The state can thus be expressed as a sum of (possibly decaying) contributions: where results from the prior delta update at time .

This representation—derived using an extended WY representation—facilitates efficient computation and memory usage.

2. Relation to Prior Delta Rules and Gating Mechanisms

Previous delta rule literature (Widrow–Hoff, associative memory models), as operationalized in DeltaNet, focuses on targeted updates, typically interpolating the new memory value along specific directions, with an update such as: where is a key vector (Yang et al., 2024). This construction helps manage interference (key collisions) and enhances associative memory, but lacks mechanisms for rapid global forgetting.

On the other hand, gating mechanisms (e.g., Mamba2) perform uniform decay: which enables efficient removal of stale content but cannot selectively overwrite particular associations.

The gated delta rule was conceived to integrate these effects so that models can both “forget fast” (via ) and “update precisely” (via ), overcoming limitations of both isolated gating and delta-based updating (Yang et al., 2024).

3. Hardware-Efficient Parallelization and WY Representation

The direct application of recurrence in the gated delta rule is inherently sequential, which impedes parallel training. The cited work implements a chunkwise parallelization leveraging an extended WY representation and UT transforms (Yang et al., 2024, Yang et al., 2024):

- The sequence is partitioned into chunks.

- Per-chunk recurrences are unrolled and computed in parallel using dense batched matrix multiplications, minimizing memory and I/O overhead.

- The WY parameterization compactly encodes products of (rank-one) Householder-like matrices, enabling memory for sequence states of dimension .

This chunkwise strategy enables high-throughput GPU training, achieving linear time complexity with minimal overhead. The approach is realized in practical kernels targeting tensor core architectures and is efficient enough to scale to 1.3B parameter LLMs over 100B tokens.

4. Empirical Performance and Practical Benefits

Gated delta rule–based networks demonstrably outperform strong linear transformer models such as Mamba2 and DeltaNet across several evaluation regimes (Yang et al., 2024):

- Language modeling: lower perplexity on standard corpora.

- Commonsense reasoning, in-context retrieval, and long-context understanding: higher accuracy, especially for tasks requiring recall and selective forgetting.

- Training throughput: parallelization strategy yields significant speed-ups with no observed loss in predictive performance.

Hybrid architectures combining Gated DeltaNet layers with sliding window attention or Mamba2 layers further extend this advantage, maintaining both rapid local modeling and robust long-range memory management.

5. Connections to Logical Inference and Other Gating-Deltas

Gated delta mechanisms have also appeared in other domains. In first-order proof calculi, the gated delta rule applies to quantifier instantiation—with side-conditions (“gates”) controlling variable assignment—contrasted with purely liberalized delta rules that maximize flexibility (0902.3730). In GRU networks, “gated delta rules” materialize as nonlinear weight-space inequalities that enforce input-to-state stability by bounding the effective “delta” between states via the gating elements (Bonassi et al., 2020).

In stochastic optimization contexts, variants such as the stochastic delta rule introduce gradient-dependent noise via parameterized means and variances, with gating emerging as multiplicative controls on updates (though without explicit probabilistic interpretation in most gating-delta frameworks) (Frazier-Logue et al., 2018).

6. Architectural Variations and Hybrid Designs

The adoption of Gated DeltaNet layers within hybrid transformer architectures reflects the complementary nature of gating and delta updates. These designs often alternate layers of Gated DeltaNet with sliding window attention or incorporate Mamba2 components, balancing global memory with local interaction modeling. Empirical evidence supports that such hybrids further bolster retrieval, reasoning, and length extrapolation performance (Yang et al., 2024).

7. Significance and Future Prospects

The gated delta rule provides a principled foundation for systems requiring both flexible memory updates and rapid information decay. Its technical realization is intimately tied to scalability on modern hardware and enhanced empirical performance in tasks demanding long-context or associative recall. Continued research explores optimal scheduling of gating/delta rates (, ), adaptive mechanisms for hybrid construction, and broader application in neural sequence modeling, control, and symbolic logic systems.

In summary, the gated delta rule encapsulates an overview of uniform gating and targeted delta-style memory updates, affording precise control over information persistence and recall, with efficient parallelization frameworks enabling its deployment in large-scale neural architectures (Yang et al., 2024).