- The paper introduces a flag decomposition technique that achieves parameter-optimal synthesis by partitioning n-qubit unitaries into a flag circuit and a diagonal operator.

- It employs both Clifford+Rot and phase gradient strategies to reduce the number of costly rotation gates and entangling operations.

- Selective de-multiplexing (SDM) is applied to further minimize circuit depth and resource counts, especially benefiting matrix product state preparation.

Parameter-Optimal Unitary Synthesis via Flag Decompositions

Overview of Flag Decomposition Framework

The paper "Parameter-optimal unitary synthesis with flag decompositions" (2603.20376) introduces the flag decomposition as a foundational technique for the parameter-optimal synthesis of generic unitaries and isometries, notably improving quantum circuit resource counts both for {Clifford + Rot} and phase gradient decompositions. The authors re-examine classical unitary synthesis techniques, emphasizing optimization in terms of the required number of parameterized rotation gates—crucial for FTQC where non-Clifford gates dominate cost.

Central to the methodology is the separation of an n-qubit unitary V∈U(2n) into a flag circuit F with 4n−2n degrees of freedom, and a diagonal operator Δ with 2n parameters. This achieves a total of 4n parameters, corresponding exactly to the manifold dimension of U(2n), thus ensuring parameter-optimality. The flag circuit resides on the complete flag manifold, realized recursively from one- and two-qubit base cases.

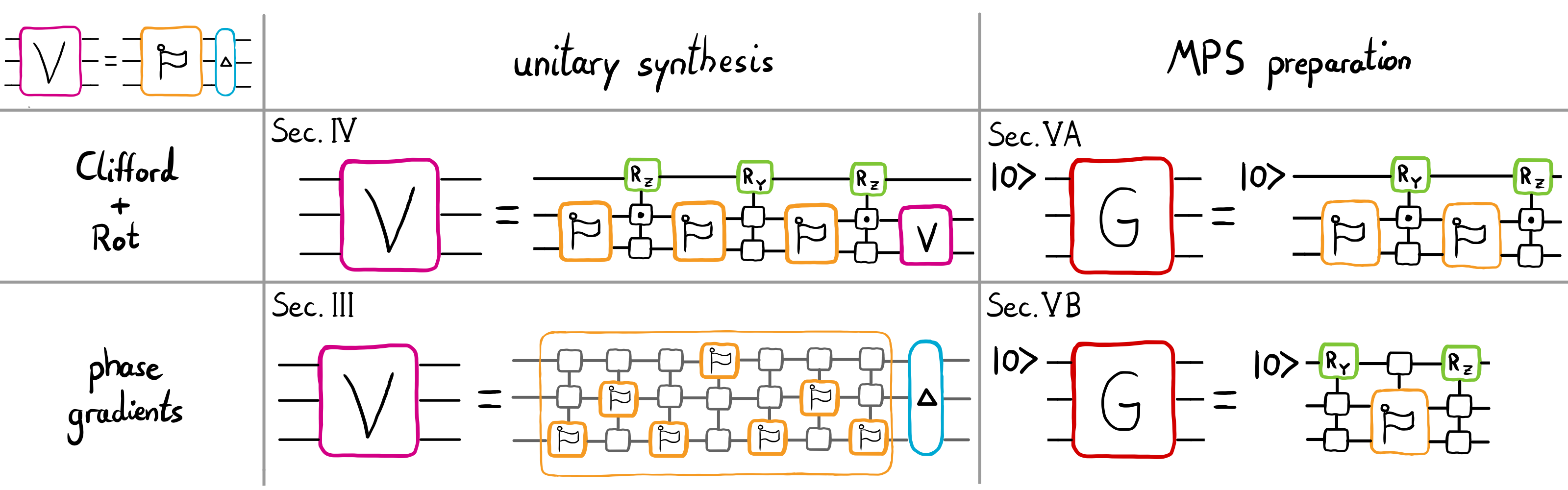

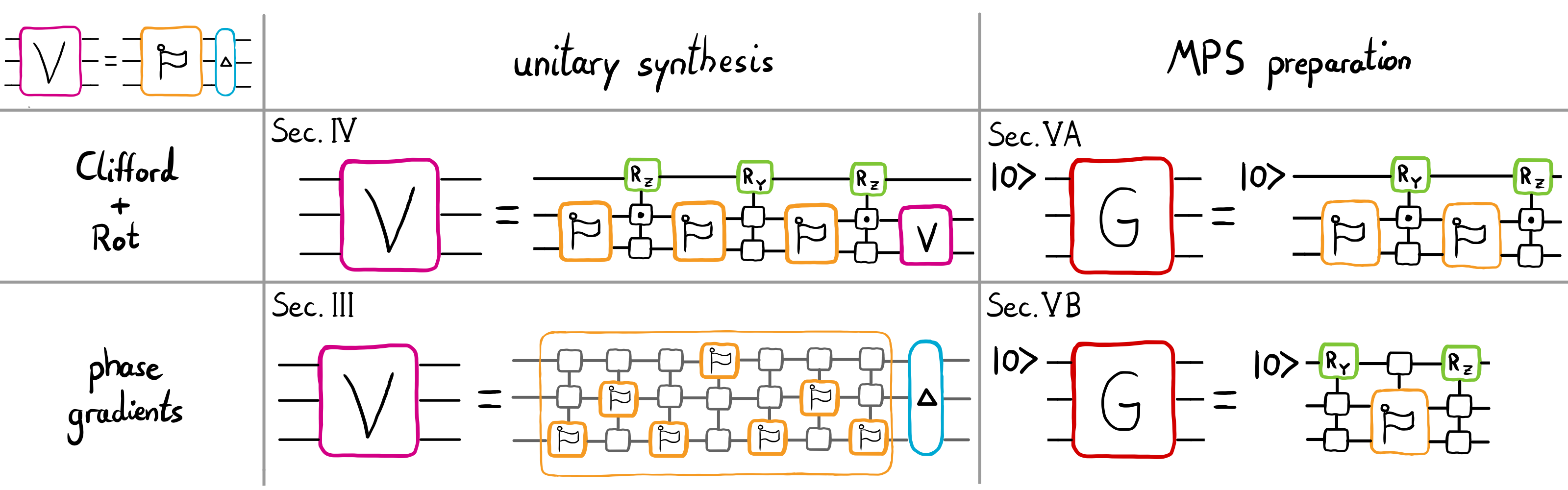

Figure 1: Flag decomposition partitions an n-qubit unitary into a flag circuit (orange, 4n−2n parameters) and a diagonal (blue, 2n parameters), enabling parameter-optimal synthesis for generic unitaries and MPS matrices across gate sets.

Clifford+Rot and Phase Gradient Decomposition Strategies

The approach is tailored to two main decomposition paradigms.

Clifford+Rot Decomposition: For NISQ devices, where CNOTs are the primary bottleneck for reliability, quantum Shannon decomposition (QSD) and block-ZXZ decomposition yield the lowest CNOT counts. However, for FTQC, optimality in parameterized rotations supersedes CNOT optimization. The recursive flag decomposition recovers the parameter-optimal circuit structure previously encapsulated, but overlooked, in Bergholm et al. (2004), matching the lower bound 4n−1 for rotations with a mildly sub-optimal CNOT count, which is further improved via the selective de-multiplexing (SDM) scheme introduced here.

Phase Gradient Decomposition: In architectures equipped with phase gradient resource states and QROM, the flag decomposition circuit facilitates efficient implementation of multiplexed rotations, removing extraneous increment/decrement operations seen in prior schemes (e.g., Berry et al. 2025). Each multiplexed flag executes via QROM loading, bitwise addition with a phase gradient state, and measurement-based uncomputation merged into subsequent flags.

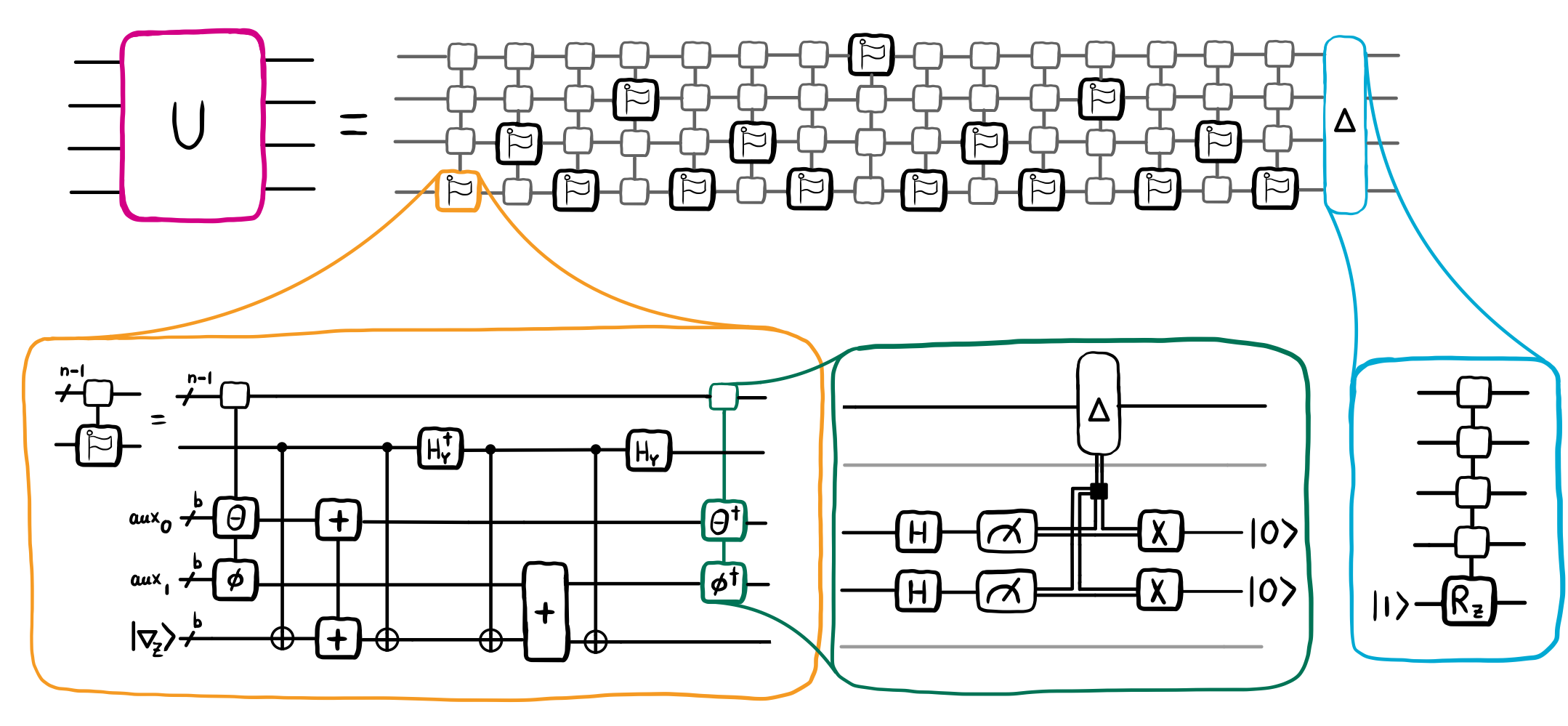

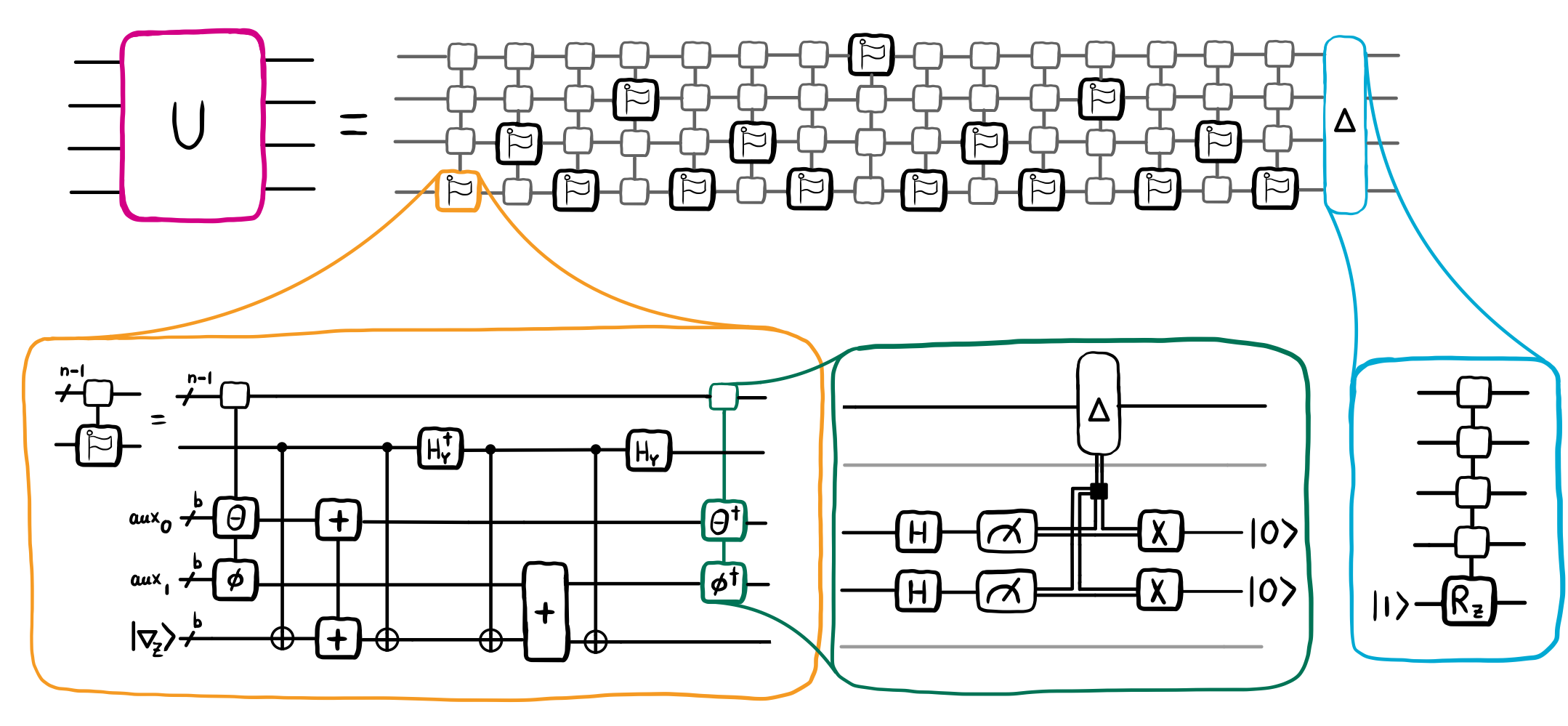

Figure 2: Phase gradient decomposition leverages recursive flag circuits, QROM loading of rotation angles, adders with phase gradient resource states, and measurement-based correction—eliminating increment/decrement overhead.

Selective De-Multiplexing: Circuit Depth and Entangler Count

The paper develops SDM as an innovation to maintain parameter-optimality while minimizing CNOTs. SDM interleaves QSD-style de-multiplexing selectively with recursive flag decompositions—selectively deconstructing multiplexers both across recursion and circuit depth. Each SDM recursion step decomposes the circuit into multiplexed parameterized rotations, flag circuits, and subunitaries, followed by symmetrized multiplexing and de-multiplexing schemes that minimize entangling operations.

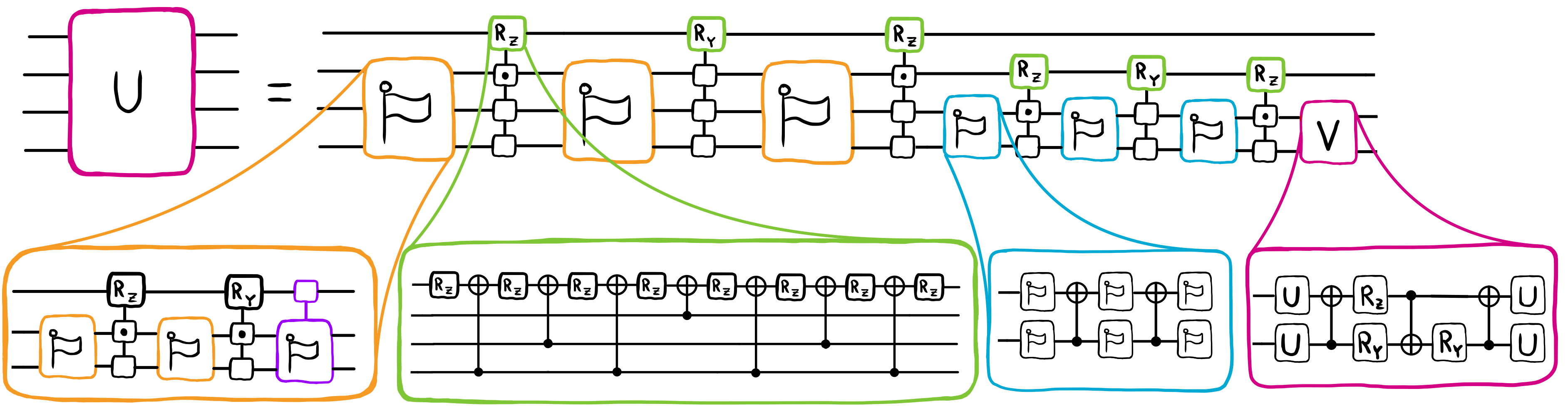

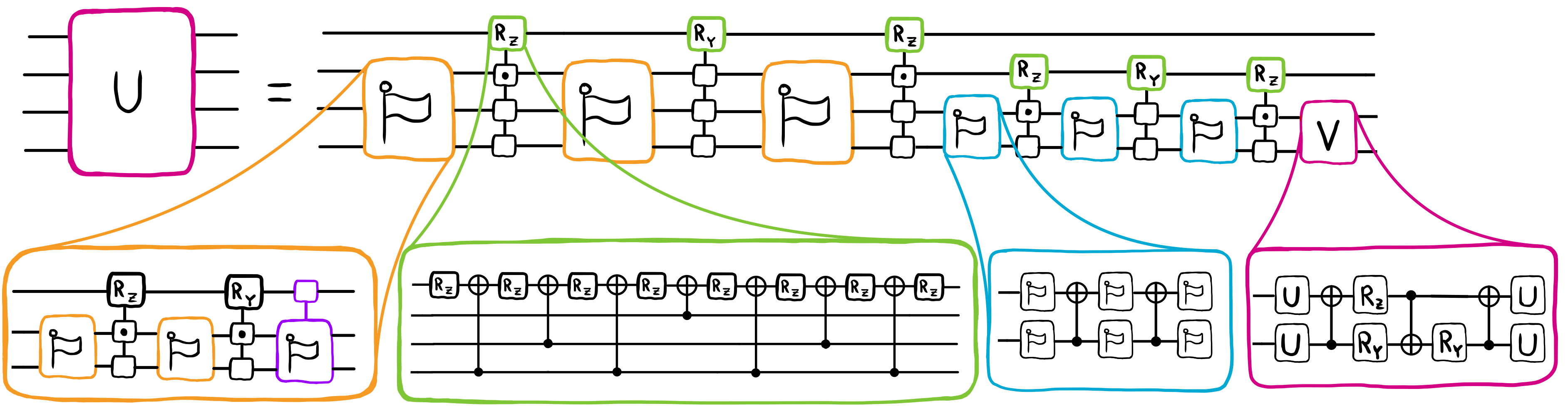

Figure 3: SDM: A unitary is decomposed with a single QSD step (top), followed by selective de-multiplexing of the flag circuit (orange), symmetrized multiplexed rotations (green), and base case decompositions (blue, magenta), with multiplexed flags decomposed recursively.

The resulting circuit achieves optimality in parameter count and CNOTs, matching or surpassing the best known results from QSD or block-ZXZ variants for n=3,4 qubits.

Application to Matrix Product State (MPS) Preparation

Flag-based unitary synthesis circuits directly translate to optimal resource counts for MPS preparation, a frequent quantum algorithm primitive. Each MPS tensor is mapped to an isometry, which is completed to a unitary acting on auxiliary registers and a fixed-state input qubit. The effective code respects both the isometric structure and gauge freedom of MPS, reducing the circuit parameter count by leveraging the removable degrees of freedom from fixed inputs and inter-tensor gauge mergeability.

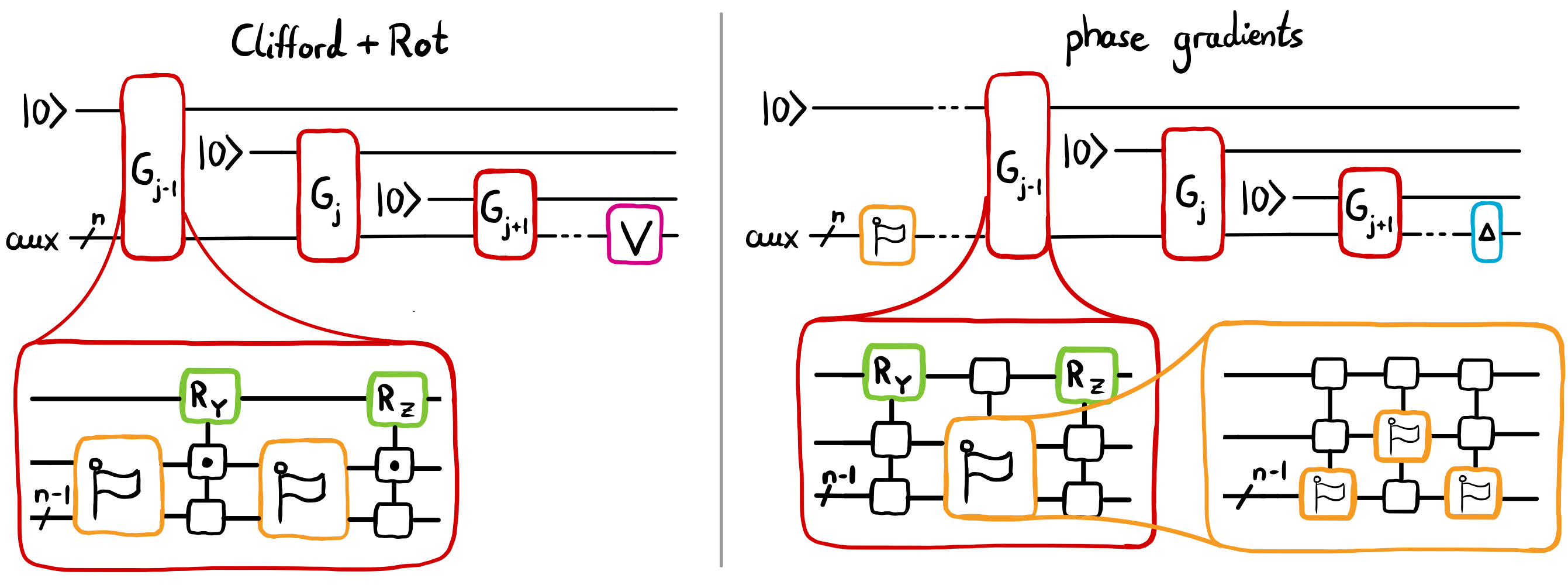

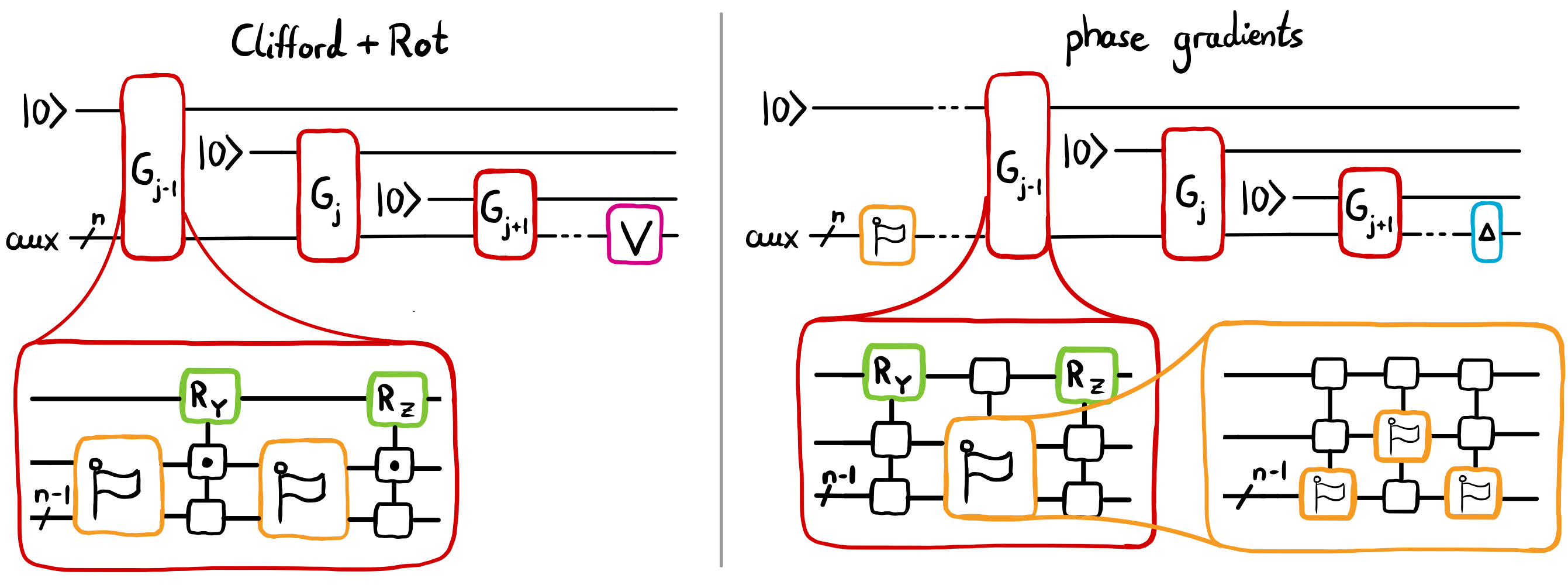

Figure 4: MPS preparation decomposes each tensor (red) into a multiplexed RY, subcircuit for reduced multiplexed unitaries, and a terminal diagonal, decomposed using Clifford+Rot or phase gradient techniques, with optimally distributed parameter counts.

The circuit for each isometry Gj achieves the theoretical lower bound of 2χ2 parameters (χ=2n bond dimension), accounting for removals due to fixed input, isometric structure, and shared gauge freedom across the auxiliary register. This improves upon prior state-of-the-art resource counts, particularly in Toffoli gates for phase gradient schemes and in CNOT count for Clifford+Rot schemes.

Technical Results and Resource Counts

- Flag Decomposition: Achieves 4n−1 Rot gates, and for Clifford+Rot synthesis, CNOT cost of 214n−432n−1, further reduced with SDM to 214n−83(n+2)2n+n−1.

- Phase Gradient Synthesis: Recursive flag circuits save one multiplexer and all increment/decrement costs, yielding substantial Toffoli savings over prior QR and QROM-based techniques.

- MPS Preparation: For both decomposition methods, the circuit matches the optimal parameter bounds, with further reductions at boundaries where isometries are of asymmetric dimensions.

Implications and Future Directions

The formalization of flag decompositions provides a unified Lie group-based framework for synthesis, reconciling recursion-based reductions with multiplicity and gauge freedom respecting parameterizations. Practically, this enables compilation routines that are scalable to relevant system sizes, with concrete resource savings in quantum chemistry and simulation applications, especially as hardware evolves to support phase gradient techniques.

Flag circuits, though previously underappreciated, are identified as the central backbone across the literature for parameter-optimal synthesis. The systematic computational toolbox the authors offer (with SciPy/PennyLane interfaces) enables practical synthesis at scale.

Future work includes:

- Exploration of lower bounds for CNOT and depth simultaneously, as suggested by recent optimal brick wall circuits.

- Hybrid compilation schemes leveraging auxiliary qubits and interplay between Clifford+Rot and phase gradient families.

- Extension of group-theoretic synthesis to specialized circuit families, including tensor network and variational circuit architectures.

Conclusion

This work rigorously establishes flag decomposition as the essential tool for parameter-optimal unitary and isometry synthesis, achieving optimal resource counts for both generic unitaries and matrix product state preparation. SDM provides further advances in circuit efficiency, extending practical applicability to large-scale quantum algorithms. The results unify mathematical structure and practical compilation, creating fertile ground for continued advances in quantum circuit synthesis and optimization.