Formal Verification Methods

- Formal Verification Methods are mathematically based techniques that rigorously establish the correctness of hardware and software systems through exhaustive state-space analysis.

- They employ methods such as model checking, deductive verification, and synthesis with specification languages like PSL and ACSL to formalize safety and liveness properties.

- Applications span digital circuits, embedded systems, and cyber-physical platforms, ensuring compliance with safety standards while uncovering critical design flaws.

Formal verification methods are mathematically based techniques used to rigorously establish the correctness of hardware and software systems. These methods enable exhaustive analysis of a design’s state space, capturing properties like safety, liveness, and security guarantees that may be elusive to testing and simulation alone. The scope of formal verification encompasses systems ranging from digital circuits and embedded controllers to complex cyber-physical and autonomy-enabled platforms. This article surveys the principles, methodologies, languages, and workflow integration strategies central to formal verification, illustrated with representative research and industrial applications.

1. Defining the Scope and Principles of Formal Verification

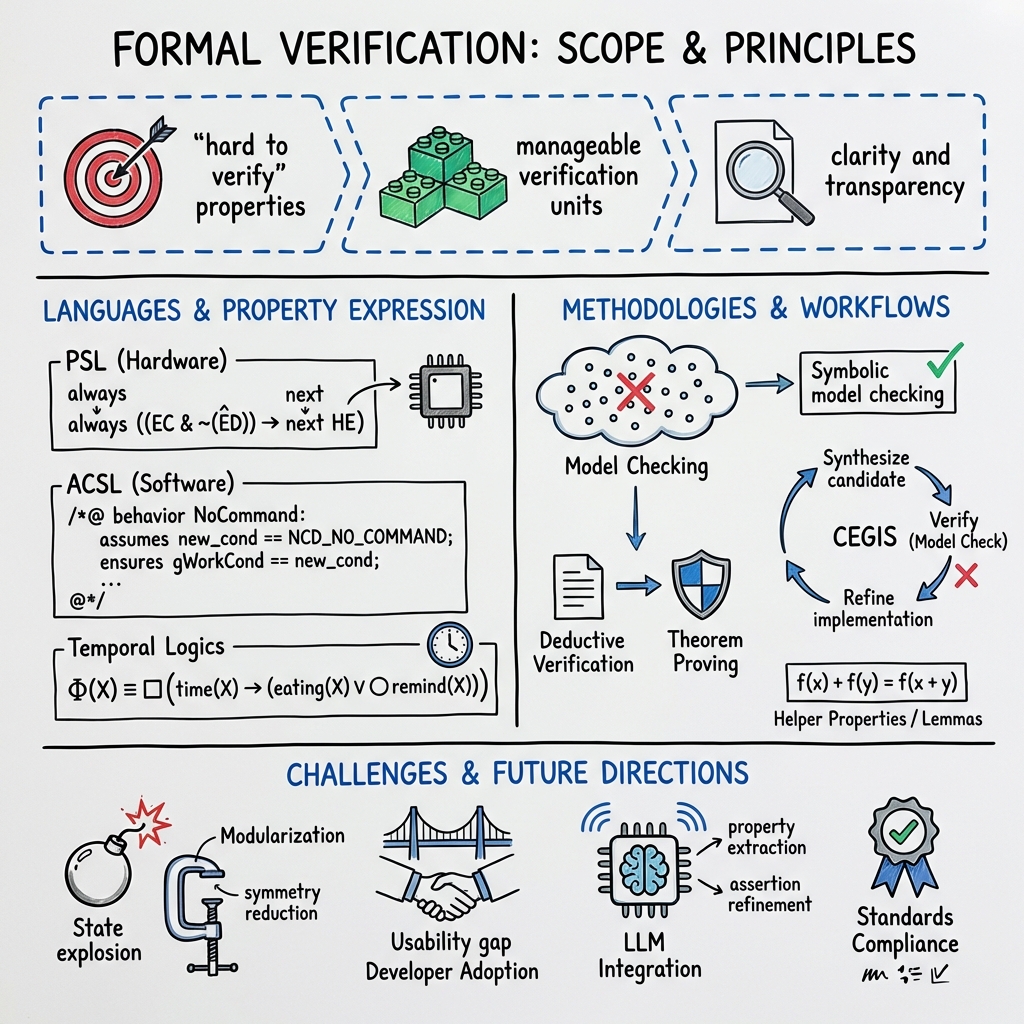

Formal verification requires a clear definition of what to verify, guided by three core practical requirements:

- The properties of interest must be hard to verify via conventional methods (e.g., rare corner cases or complex error propagation).

- The verification must address manageable verification units (modular, leaf-level, or small components), mitigating state-space explosion.

- There must be clarity and transparency in what is being verified, ensuring ease of specification, review, and collaboration among stakeholders (0710.4848).

Exhaustive verification requires partitioning system properties into stereotype categories. For example, when validating data integrity in server chips, properties are decomposed into (i) error detection ability, (ii) soundness of internal states, and (iii) output data integrity. Each category is addressed locally at the block/module level, facilitating a divide-and-conquer approach that is tractable for formal tools.

2. Formal Specification Languages and Property Expression

Specification languages play a critical role in formulating verifiable properties:

- PSL (Property Specification Language): Adopted for hardware property expression, PSL supports assertions such as temporal properties (“always”, “next”). For example:

1 |

always ((EC & ~(^ED)) -> next HE) |

- ACSL (ANSI C Specification Language): Enables C code annotation with formal assertions, pre/postconditions, and behavior descriptions, supporting deductive verification at the code level. For example:

1 2 3 4 5 6

/*@ behavior NoCommand: assumes new_cond == NCD_NO_COMMAND; ensures gWorkCond == new_cond; ... @*/ void cbit_set_work_cond(uint16_t new_cond); - Temporal Logics: Linear Temporal Logic (LTL) and CTL are used to encode safety and liveness statements, e.g., used for model checking of behavioral properties (Winikoff, 2019).

- Domain-Specific Extensions: Libraries and block-based property templates (e.g., Why3 theories for Simulink blocks) modularize the semantics of functional constructs, enabling automated translation and proof goals for control and cyber-physical systems (Araiza-Illan et al., 2014).

3. Methodologies and Tool Architectures

A range of approaches structure the formal verification workflow:

- Model Checking: Exhaustively explores all system states to verify temporal properties. Symbolic model checking (e.g., with SAT/SMT solvers or BDDs) is used for both hardware and software protocols. For example, the use of Cadence JasperGold for bounded and unbounded proofs (via k-induction) on ECC designs (Kumar, 2024).

- Deductive Verification/Theorem Proving: Properties are specified as theorems, and their proof is constructed either interactively or automatically (using, for instance, Why3 or PVS with SMT backends). The mapping from models (such as Simulink) into the proof assistant's language is systematically managed by translation tools and theory libraries (Araiza-Illan et al., 2014, Pang et al., 2015).

- Counterexample-Guided Inductive Synthesis (CEGIS): Automates code synthesis by iteratively generating candidate solutions and using model checking to refute incorrect ones, refining the implementation until it satisfies all formal constraints (Weiß et al., 2021).

- Helper Properties, Invariants, and Lemmas: For complex or sequential systems, proofs may not converge until additional auxiliary assertions are provided, such as the linearity property of syndrome generators in ECC verification: . These helper properties restrict the state space and enable unbounded proofs feasible within practical time bounds (Kumar, 2024).

- Parameterization and Inductive Reasoning: Verification of parameterized or distributed systems employs frameworks (e.g., wiseParaverifier) that generalize from small instances (concretizations) and synthesize inductive invariants using both heuristic generalization and symmetry reduction, managing invariants involving mixed quantification (Forall/Exists) (Xiu et al., 23 Mar 2025).

4. Application Domains and Case Studies

Formal verification impacts a diversity of industrial and academic settings:

- Hardware Data Integrity and Safety: Decomposition of RAS property checks for server chip RTL; 2047 PSL properties verified in 20 hours, with seven critical bugs found—of which more than half were not easily detectable with simulation (0710.4848).

- Safety-Critical Control Systems: For programmable logic controllers (PLCs), approaches combine requirements formalization—using cause-and-effect matrices, state machines, and logic assertions—with model-checking and simulation to validate safety against IEC61511/IEC61508 standards (Lopez-Miguel et al., 26 Feb 2025). Service-based verification models (as at CERN/GSI) enable third-party verification without extensive in-house expertise.

- Real-Time Function Blocks: In the nuclear domain, composite function blocks with on-delay timers are verified compositionally. Handling timing tolerances and proof of initialization/feedback correctness is critical (Pang et al., 2015).

- Software and Avionics: ACSL/Frama-C annotation of sensor control functions in avionics demonstrates effective LLR formalization, though challenges remain regarding proof obligation complexity and modeling of internal/hardware state (Dordowsky, 2015).

- Formal Verification in the PLC Domain: Tools such as Fastsynth integrate with Siemens TIA Portal, leveraging self-configuring blocks and constraint lists with CEGIS-based synthesis, supporting efficient model checking for industrial applications (Weiß et al., 2021).

- Mixed-Signal Design: AMS IP verification introduces specific challenges, requiring abstraction and formal-friendly digitalized models for analog blocks. Automatic property generation with metamodeling frameworks and k-induction for state-space management are pivotal (Mohanty et al., 2024).

5. Addressing Scalability, Usability, and Integration Challenges

Formal verification methods contend with:

- Scalability: State explosion is mitigated by modularization, combinatorial reductions, use of abstract models, and heuristic helper invariants (e.g., abstract models for ECC encoders/decoders (Kumar, 2024), or symmetry reduction in parameterized verification (Xiu et al., 23 Mar 2025)).

- Usability and Developer Adoption: Bridging the usability gap requires close alignment with familiar development workflows. Initiatives such as integrating formal verification backends with property-based testing frameworks (e.g., Rust proptest, KLEE, Crux) and focusing on positive weekly cost-benefit ratios are proposed (Reid et al., 2020).

- Explainability of Results: Structured counterexample explanation improves comprehension for practitioners, as shown in automotive engineering studies at Bosch (Kaleeswaran et al., 2023). Tooling must provide accessible explanations to foster broader adoption.

- Human-in-the-Loop and LLM Integration: LLMs are increasingly used to automate property extraction from requirements and generate helper assertions (e.g., SpecVerify integrating Claude 3.5 Sonnet and ESBMC for cyber-physical systems, or LLM-driven assertion refinement for hardware induction proofs (Wang et al., 7 Jul 2025, Kumar et al., 2024)). Nevertheless, high-quality requirements and human oversight remain essential due to occasional misinterpretation or overgeneralization by AI models.

6. Standards Compliance, Impact, and Future Directions

Formal verification directly supports compliance with safety and functional standards (e.g., ISO 26262, IEC 61511/61508, DO-178C). The use of formalized requirements, compositional proofs, and traceable property specifications underlies certification in domains including automotive electronics, industrial automation, avionics, and space systems (0710.4848, Lopez-Miguel et al., 26 Feb 2025, Luckcuck et al., 2021).

Future efforts are anticipated in:

- Extending tool integration, model coverage (including integration with simulation-based flows and model-based design), and support for broader property classes (robustness, performance, non-linear dynamics).

- Enhancing parameterized verification by automating invariant generation and leveraging symmetry at scale.

- Experimenting with generative AI for requirements translation, invariant discovery, and assertion refinement, while maintaining human-in-the-loop validation.

- Developing meta-model based, domain-specific property templates and libraries for increased modularity and maintainability.

Formal verification continues to evolve by balancing mathematical rigor with pragmatic integration into industrial development processes, supported by automation, modular property expression, and a continual focus on scalability and usability.