Search Smarter, Not Harder: A Scalable, High-Quality Zoned Neutral Atom Compiler

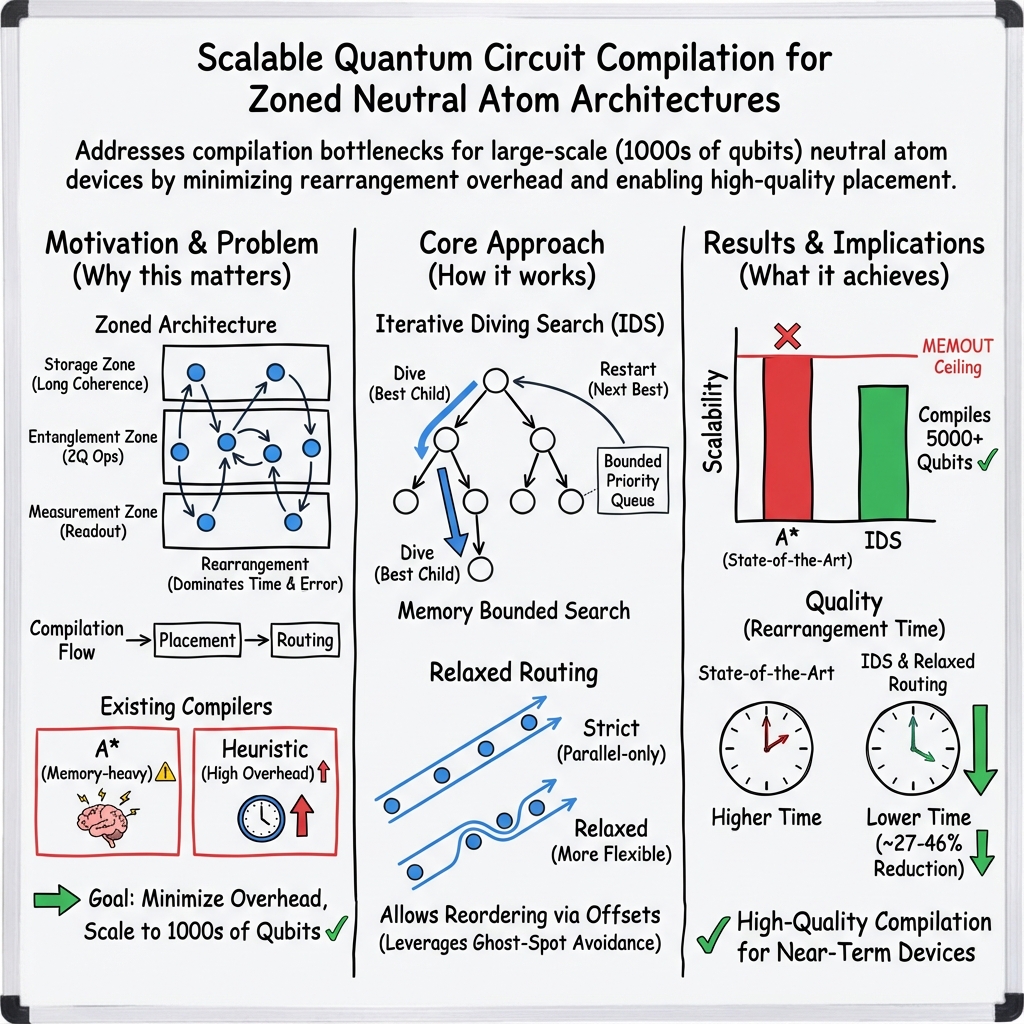

Abstract: Zoned neutral atom architectures are emerging as a promising platform for large-scale quantum computing. Their growing scale, however, creates a critical need for efficient and automated compilation solutions. Yet, existing methods fail to scale to the thousands of qubits these devices promise. State-of-the-art compilers, in particular, suffer from immense memory requirements that limit them to small-scale problems. This work proposes a scalable compilation strategy that "searches smarter, not harder". We introduce Iterative Diving Search (IDS), a goal-directed search algorithm that avoids the memory issues of previous methods, and relaxed routing, an optimization to mitigate atom rearrangement overhead. Our evaluation confirms that this approach compiles circuits with thousands of qubits and, in addition, even reduces rearrangement overhead by 28.1% on average. The complete code is publicly available in open-source as part of the Munich Quantum Toolkit (MQT) at https://github.com/munich-quantum-toolkit/qmap.

Paper Prompts

Sign up for free to create and run prompts on this paper using GPT-5.

Top Community Prompts

Explain it Like I'm 14

Overview

This paper is about making quantum computers based on neutral atoms run big programs more efficiently. Think of a “compiler” as a smart translator that turns a high-level plan (a quantum circuit) into step-by-step instructions the machine can actually do. The authors focus on a special kind of neutral-atom machine that has different areas (zones) for different jobs, like “store,” “entangle,” and “measure.” They introduce a new way to compile programs that handles thousands of qubits, uses less memory, and finishes faster. Their key idea is to “search smarter, not harder” by using a goal-directed search method called Iterative Diving Search (IDS), plus an optimization called relaxed routing to reduce how much the atoms have to be moved around.

Key Objectives and Questions

- Can we design a compiler that works well even for very large quantum circuits (with thousands of qubits)?

- How do we reduce the extra time spent moving atoms around (called rearrangement overhead), which slows down the computation and can cause more errors?

- Can we avoid the huge memory use of previous methods and still get high-quality results?

How Did They Do It?

Think of the machine like a big grid of tiny traps, each holding one atom (a qubit). There are different zones:

- Storage zone: safe parking spot for atoms when they’re not interacting.

- Entanglement zone: where pairs of atoms get close enough to interact (do a two-qubit gate).

- Measurement zone: where the result is read out.

Running a quantum program involves repeatedly:

- Doing any single-qubit operations that are ready.

- Moving pairs of atoms into the entanglement zone so they can interact.

- Doing the two-qubit operations.

- Moving atoms back to storage if they’re not needed.

- Measuring when the program says to.

Moving atoms is tricky because:

- Rows and columns of movable traps can’t cross or split.

- Activating multiple rows/columns can create “ghost spots” (accidental traps), which must be avoided.

The main challenge is arranging and moving many atoms at once without breaking those rules, and doing it with as few “rearrangement steps” as possible. Fewer steps means less time and fewer errors.

Here’s their approach in everyday terms:

- Routing-aware placement: When deciding where to put atoms for the next step, don’t just pick the shortest path. Instead, choose positions that make it easy to move many atoms at the same time without conflicts. This increases parallel movement and cuts the number of steps.

- Smarter search (IDS): Previous compilers used a method called A*, which explores a ton of possible arrangements and keeps many of them in memory, which can easily explode to tens of gigabytes. IDS, on the other hand, dives deep down the most promising path first (like exploring one hallway thoroughly before trying others), keeps a small shortlist of backup options, and only stores a limited number of possibilities. This makes it much more memory-friendly while still finding high-quality solutions.

- Relaxed routing: To avoid ghost spots, older methods moved atoms row-by-row in a strict order. Relaxed routing allows reordering rows and columns during the movement by inserting small “offset moves” at smart times. This flexibility lets more atoms move together in fewer steps, especially when atoms are far apart. For short distances, they estimate whether relaxed routing helps; if not, they stick to the strict approach.

Main Findings and Why They Matter

- Scalability: The new compiler successfully handled circuits with up to about 5,000 qubits and up to 300 two-qubit gates in parallel per layer. The previous state-of-the-art often ran out of memory on much smaller problems.

- Less rearrangement time: On average, the new method reduced the time spent moving atoms by about 27.1% compared to the previous best method. When also using relaxed routing, the average improvement rose to about 28.1%. On some highly parallel cases, the improvement was as high as around 45%.

- Practical performance: The new approach compiled all tested circuits within minutes without hitting memory limits, while the old method frequently crashed due to memory out-of-bounds.

Why it matters: Reducing rearrangement time directly lowers the total run time and exposure to errors (like decoherence). Shorter, smoother runs make the results more reliable. And being able to compile huge circuits is essential as neutral-atom machines scale up.

Implications and Impact

- For researchers and engineers: This compiler lets them plan and run bigger quantum programs on neutral-atom hardware without being blocked by memory and time overheads. It’s open-source, so others can use and improve it.

- For the path to large-scale quantum computing: As neutral-atom systems grow to thousands of qubits, smart compilation becomes critical. IDS and relaxed routing show that better algorithms can unlock the hardware’s potential, making complex, highly parallel quantum circuits practical.

- For future work: The general idea—goal-directed search with limited memory plus movement-aware placement—could inspire similar strategies on other quantum platforms and lead to even better compilers as hardware evolves.

Knowledge Gaps

Knowledge gaps, limitations, and open questions

Below is a single, focused list of what remains missing, uncertain, or unexplored, designed to be actionable for future researchers:

- Lack of formal guarantees: no theoretical bounds on IDS’s solution quality, optimality gap, or worst-case time/memory complexity relative to A* or other search methods.

- Unspecified IDS hyperparameters: key controls like the priority-queue cap and the number of trials are not reported nor systematically studied for their impact on quality, runtime, and memory.

- Heuristic robustness: the chosen heuristic parameters () are tuned empirically on a subset of circuits; there is no adaptive or generalizable tuning strategy across diverse workloads.

- Missing ablations: no isolation of individual contributions from scheduling, reuse analysis, IDS, and relaxed routing; need ablation studies to quantify each stage’s influence on rearrangement overhead.

- Generalizability to other architectures: evaluation assumes a specific two-zone layout, trap spacings, and capacities; it is unclear how IDS and relaxed routing perform on:

- different zone geometries (e.g., multiple entanglement zones, non-rectangular grids),

- alternative trap densities/spacing, or

- different minimum separations and AOD/SLM constraints.

- Hardware validation: results are simulation-only; no on-hardware demonstrations or validation against real AOD control latencies, laser timing jitter, calibration drift, and atom loss.

- Incomplete error modeling: rearrangement time is used as a proxy for fidelity, but end-to-end error sources (idle exposure in entanglement zone, crosstalk, Rydberg beam spillover, gate and measurement errors) are not quantified or modeled.

- Exposure analysis: the effect of relaxed routing and IDS placements on time spent under global beams (and resulting error rates) is not measured.

- Constraint correctness for relaxed routing: there is no formal proof that relaxed routing always satisfies non-crossing, preservation, and ghost-spot constraints under all movement sequences; counterexamples and edge cases remain unexamined.

- Crossover threshold estimation: the distance-based decision to apply relaxed routing vs. strict routing is heuristic; no analytical or experimentally validated model exists to predict the crossover point across hardware settings.

- Concurrency limits: real systems may limit the number of simultaneously activated rows/columns or impose bandwidth constraints on AOD control; IDS/routing assume parallel pick-up/drop-off without modeling such limits.

- Defective traps and atom loss: robustness of IDS and routing in the presence of missing/defective traps, atom loss during rearrangement, and reloading operations is unaddressed.

- Multi-zone and large-scale coordination: compilation for architectures with multiple entanglement/measurement zones, inter-zone synchronization, and long-distance shuttling is not explored.

- Scheduling co-optimization: scheduling is treated as fixed; joint optimization of scheduling, placement, and routing to reduce peak parallel CZ counts and rearrangement pressure is not studied.

- Mid-circuit measurement and feed-forward: support for circuits with frequent measurements, conditional operations, and real-time feedback (critical for neutral-atom platforms) is not addressed.

- Benchmark representativeness: beyond graphstate and MQT Bench circuits, the evaluation lacks workloads tailored to neutral-atom strengths (e.g., highly parallel Clifford circuits, error-correcting code routines, chemistry with high entanglement bandwidth).

- Scalability beyond 306 parallel gates: the entanglement-zone capacity caps parallelism at 306 CZs; strategies for scaling beyond this (e.g., multi-zone concurrency or temporal tiling) are not considered.

- Movement profile assumptions: constant jerk and maximum velocity are assumed; sensitivity to different motion profiles, hardware-limited acceleration, and vibration-induced errors is not analyzed.

- Step count vs. distance trade-offs: IDS optimizes rearrangement time, but the relationship among number of rearrangement steps, average movement distance, and fidelity impact is not separately quantified.

- Measurement-stage optimization: movement to and within measurement zones, readout timing, and their contribution to total error are not optimized nor evaluated.

- Code-generation fidelity: correctness and timing of the hardware-specific instruction sequence (including laser multiplexing and beam scheduling) are not validated or benchmarked.

- Portability and performance: evaluation is limited to an Apple M3 with 16 GB RAM; cross-platform performance, multi-core scaling, and GPU/accelerator opportunities are not assessed.

- Integration with fault tolerance: mapping constraints for error-correcting codes (e.g., surface code style layouts, stabilizer measurement schedules) and compiler support for fault-tolerant protocols are not addressed.

- Learning-based search: alternative search strategies (beam search, Monte Carlo tree search, learned heuristics) are not compared; opportunities for data-driven or adaptive search remain open.

- Open-source reproducibility: the heuristic and cost functions reused from prior work are not fully specified here; complete, reproducible descriptions and configuration files are needed for independent validation.

Practical Applications

Immediate Applications

The paper introduces a scalable, high‑quality compiler for zoned neutral atom quantum computers (Iterative Diving Search, IDS) and a “relaxed routing” optimization that cuts rearrangement overhead by ~28% on average and compiles circuits with thousands of qubits. The following applications can be deployed now, leveraging the open-source implementation in MQT qmap.

- Neutral‑atom compiler backend upgrades (Sector: software, quantum hardware)

- Use IDS as a drop‑in backend to replace A* in existing toolchains (e.g., integrate via MQT qmap into Qiskit, tket, Cirq, AWS Braket/QuEra backends) to increase circuit size and improve fidelity by reducing rearrangement time.

- Tools/products/workflows: MQT qmap backend; “IDS placement + relaxed routing” pass; device profile import.

- Assumptions/dependencies: Zoned neutral‑atom targets; access to backend topology/zone geometry; cost/heuristic tuned to device.

- On‑the‑fly compilation on lab controllers (Sector: lab automation, software)

- Run IDS on embedded PCs/FPGAs/edge controllers for experiment scheduling without exhausting RAM, enabling larger in‑lab experiments and faster iteration.

- Tools/products/workflows: Control‑stack plugin that compiles per‑shot circuits; memory‑bounded IDS (fixed queue size); real‑time routing policy switch.

- Assumptions/dependencies: Control stack hooks for compilation; timing budgets compatible with IDS compile times; movement API supports row/column reordering.

- Cloud service quality and capacity uplift (Sector: cloud quantum services)

- Offer larger circuits and better effective fidelities on neutral‑atom cloud backends by reducing rearrangement overhead; publish new SLAs/benchmarks (e.g., graph‑state throughput).

- Tools/products/workflows: New transpiler tier (“parallelism‑aware”); billing/pricing tied to rearrangement time; public benchmarks.

- Assumptions/dependencies: Provider adoption; device supports relaxed routing; validation on production hardware.

- High‑parallelism algorithm prototyping at scale (Sector: academia, software)

- Compile graph states, QAOA, VQE, QPE, QFT with hundreds of parallel CZs and up to 5k qubits for research/benchmarking.

- Tools/products/workflows: MQT Bench + qmap pipelines; parameter sweeps for heuristic tuning (δ, β, α).

- Assumptions/dependencies: Access to devices/simulators with zoned layouts; realistic error models to map rearrangement time to fidelity.

- Device characterization and co‑design (Sector: hardware R&D)

- Use rearrangement time as a quantitative KPI to compare zone sizes, trap spacings, and AOD control profiles; optimize entanglement‑zone capacity vs. movement conflicts.

- Tools/products/workflows: Design‑space exploration with IDS; synthetic workloads (graphstate, QAOA grids); routing conflict heatmaps.

- Assumptions/dependencies: Accurate movement profiles (jerk/speed limits); ghost‑spot constraints; architecture parameters (e.g., 90% filling) configurable.

- Distance‑aware routing policy selection (Sector: hardware operations)

- Deploy the “strict vs relaxed” hybrid routing policy: apply relaxed routing for long moves (where its offset move pays off) and fall back to strict routing for short moves.

- Tools/products/workflows: Runtime selector based on estimated distance/crossover; policy telemetry.

- Assumptions/dependencies: Calibrated crossover threshold per device; control firmware supports partial row/column reordering.

- Education and workforce training (Sector: education, daily life for learners)

- Teach hardware‑aware compilation, search‑based placement, and routing under physical constraints using the open-source code and notebooks.

- Tools/products/workflows: Course labs with MQT qmap; visualization of rearrangement steps/constraints; parameter studies.

- Assumptions/dependencies: Access to standard dev environments; curated examples matching classroom resources.

- Cost and energy savings in compilation workflows (Sector: software operations, ESG)

- Reduce transpilation compute cost by avoiding memory‑hungry A* searches; improve lab energy usage by shortening laser on‑time via fewer rearrangement steps.

- Tools/products/workflows: Compiler telemetry dashboards; energy/laser duty‑cycle tracking tied to routing outputs.

- Assumptions/dependencies: Provider telemetry availability; energy/accounting models aligned with laser and AOD duty cycles.

- Benchmarking and procurement criteria (Sector: industry/consortia)

- Include “rearrangement time per layer” and “max parallel CZ compiled” as procurement/benchmark metrics for neutral‑atom systems.

- Tools/products/workflows: Public benchmark suites; certification reports using IDS outputs.

- Assumptions/dependencies: Community agreement on KPIs; reproducible benchmark environments.

- Vendor toolchain productization (Sector: quantum software vendors)

- Package IDS + relaxed routing as a supported “Neutral‑Atom Optimization Suite” (e.g., via Munich Quantum Software Company) for device OEMs and cloud providers.

- Tools/products/workflows: Commercial SDK with device adapters; support SLAs.

- Assumptions/dependencies: Licensing, maintenance resources; integration agreements with OEMs.

Long‑Term Applications

These opportunities require further research, hardware maturity, or scale-up beyond current devices.

- Fault‑tolerant scheduling with QEC (Sector: healthcare, materials, finance via robust QC)

- Integrate IDS with error‑correction schedules (e.g., syndrome extraction, lattice surgery on neutral atoms) to minimize rearrangement during QEC cycles.

- Tools/products/workflows: QEC‑aware cost functions; joint placement of data/ancilla; time‑constrained routing.

- Assumptions/dependencies: Availability of logical qubits; QEC protocols tailored to zoned architectures; long coherence and stable operations.

- Real‑time adaptive compilation/feedback (Sector: lab automation, control)

- Closed‑loop compilation that adjusts placements/routing based on live calibration, drift, or atom loss; recoverability via rapid re‑mapping.

- Tools/products/workflows: Streaming IDS with rolling horizon; health‑aware heuristics; fast re‑synthesis.

- Assumptions/dependencies: Low‑latency telemetry; robust, incremental compilation; predictable control stack timing.

- Multi‑zone/module orchestration at 10k+ qubits (Sector: quantum hardware)

- Global compiler that coordinates many entanglement/storage/measurement zones and modules, maximizing cross‑zone parallelism and minimizing congestion.

- Tools/products/workflows: Hierarchical IDS; inter‑zone routing and buffering; multi‑AOD conflict models.

- Assumptions/dependencies: Modular neutral‑atom hardware; high‑bandwidth control of many zones; scalable calibration.

- Neutral‑atom IR and standards (Sector: policy, software)

- Standardize IR extensions (OpenQASM 3, QIR) to encode zone metadata, movement constraints, and routing hints for portability and verification.

- Tools/products/workflows: Spec proposals; compiler conformance tests; reference backends.

- Assumptions/dependencies: Industry/government coordination; IP/patent considerations; safety and verification frameworks.

- Vertical application accelerators (Sector: energy, logistics, finance, chemistry)

- Domain‑specific circuit templates that exploit high parallel CZ (e.g., MBQC graph states, grid‑structured QAOA for power grids/logistics, chemistry ansätze mapped to zones).

- Tools/products/workflows: Template libraries; IDS‑tuned placements for domain topologies; co‑designed error mitigation.

- Assumptions/dependencies: Hardware fidelity/scale sufficient for advantage; domain formulations matched to neutral‑atom strengths.

- Firmware‑level AOD primitives (Sector: hardware/firmware)

- New control primitives for safe row/column reordering, ghost‑spot‑aware sequencing, and calibrated offset moves to unlock relaxed routing at scale.

- Tools/products/workflows: Microcode libraries; safety interlocks; verification tests.

- Assumptions/dependencies: Vendor engineering roadmaps; reliability in presence of ghost spots; safety certifications.

- ML‑guided heuristics and cost models (Sector: AI for systems)

- Learn IDS heuristics/costs from device logs to further reduce search and improve quality; per‑device specialization.

- Tools/products/workflows: Data pipelines; offline/online training; guardrails for worst‑case behavior.

- Assumptions/dependencies: Data availability/quality; reproducibility; robustness to distribution shift.

- Certification and regulation of compilation toolchains (Sector: policy, compliance)

- Establish certification for hardware‑aware compilers used in critical sectors; require reporting of routing‑related error budgets.

- Tools/products/workflows: Compliance tests; third‑party audits; performance attestations.

- Assumptions/dependencies: Regulatory interest; harmonized metrics; industry adoption.

- Energy and lifecycle optimization (Sector: energy/ESG, hardware ops)

- Use reduced rearrangement and optimized laser duty cycles to lower energy, extend component lifetime, and report carbon footprints for quantum jobs.

- Tools/products/workflows: Energy models tied to routing plans; job‑level CO2 reporting.

- Assumptions/dependencies: Validated power models; metering; provider transparency.

- Cross‑architecture generalization (Sector: software, hardware)

- Adapt IDS to other movement‑constrained platforms (trapped‑ion shuttling, photonic switching networks), enabling a unified hardware‑aware compilation stack.

- Tools/products/workflows: Pluggable constraint/cost modules; architecture adapters.

- Assumptions/dependencies: Accurate constraint models for other platforms; collaboration with vendors.

Glossary

- A* algorithm: A heuristic graph-search algorithm that uses a cost-plus-heuristic evaluation to find low-cost solutions efficiently. "employs the A* algorithm~\cite{hartFormalBasisHeuristic1968} to search for a low-cost goal node in the search tree."

- Acousto-Optic Deflector (AOD): A beam-steering device enabling dynamic optical traps; used to pick up, move, and drop neutral-atom qubits. "Two orthogonal AODs create a rectangular grid of adjustable traps where each row and column of the grid can be controlled individually."

- Constant jerk: A motion profile with constant rate of change of acceleration, used to constrain shuttling dynamics. "a movement profile based on a constant jerk of \SI{0.44}{\nano\meter\per\second\cubed} with a maximum speed of \SI{1.1}{\micro\meter\per\micro\second}."

- Controlled phase gate (CZ gate): A native two-qubit entangling operation in neutral-atom systems implementing a controlled-Z phase. "Two-qubit operations such as the controlled phase gate (CZ gate), the common native entangling operation on neutral atom architectures, are realized by the Rydberg blockade mechanism~\cite{everedHighfidelityParallelEntangling2023,bluvsteinLogicalQuantumProcessor2023}."

- Decoherence: The loss of quantum coherence due to environmental interactions, degrading computational fidelity. "To mitigate errors caused by decoherence, minimizing the overall computation time of a quantum computation is crucial."

- Depth-First Search (DFS): A search strategy that explores paths to leaf/goal nodes before backtracking; IDS adopts a DFS-like expansion order. "This behavior resembles a Depth-First Search~(DFS) with the important aspect that the most promising child node, according to the heuristic, is always selected for expansion."

- Entanglement zone: A designated region where two-qubit operations are executed under Rydberg excitation. "when illuminating the entire entanglement zone with a Rydberg laser, all atoms within that zone are excited to the Rydberg state."

- Ghost-spot constraint: A routing constraint that forbids creating unintended traps (“ghost-spots”) during AOD actuation. "Ghost-spot constraint"

- Ghost-spots: Unintended optical traps formed during multi-row/column actuation that can capture atoms unintentionally. "Unwanted, so-called ghost-spots, must be avoided (cf.~\cref{fig:constraint:ghost-spots})."

- Interaction radius: The maximum distance over which Rydberg-excited atoms can effectively interact. "it ensures that only qubits within a certain interaction radius of each other interact, while all illuminated atoms, also isolated ones, experience a certain likelihood of an error."

- Iterative Diving Search (IDS): A goal-directed, memory-bounded search strategy that dives along promising paths and restarts iteratively. "We introduce Iterative Diving Search~(IDS), a goal-directed search algorithm that avoids the memory issues of previous methods, and relaxed routing, an optimization to mitigate atom rearrangement overhead."

- Measurement zone: A dedicated region for qubit readout with appropriate optical access and stability. "and measurement zones for readout~\cite{bluvsteinLogicalQuantumProcessor2023,bluvsteinArchitecturalMechanismsUniversal2025}."

- Minimum weight perfect matching: A graph-optimization technique that assigns pairs to minimize total weight; used as a fast but suboptimal placement heuristic. "ZAC employs a fast but suboptimal placement strategy based on minimum weight perfect matching."

- Non-crossing constraint: A routing rule that forbids AOD-controlled rows/columns from crossing during movement. "Non-crossing constraint"

- Optical tweezers: Highly focused laser beams used to trap and position individual neutral atoms. "The atoms are trapped by optical tweezers or lattices~\cite{barredoAtombyatomAssemblerDefectfree2016}."

- Preservation constraint: A routing rule stating activated rows/columns cannot split or merge during shuttling. "Preservation constraint"

- Relaxed routing: A routing approach that allows reordering rows/columns during a rearrangement to increase parallelism and reduce steps. "We call this new approach relaxed routing in contrast to the established strict routing."

- Rearrangement constraints: The set of physical/operational rules governing simultaneous atom movements (e.g., non-crossing, preservation, ghost-spot avoidance). "the following rearrangement constraints must be followed~\cite{stadeAbstractModelEfficient2024}:"

- Rearrangement overhead: The time cost added by atom movements between zones, directly affecting circuit fidelity. "On zoned neutral atom architectures, this translates directly into minimizing the rearrangement overhead, i., the time spent rearranging atoms between layers."

- Rearrangement step: A single pick-up–move–drop-off cycle grouping parallel atom shuttles under constraints. "One so-called rearrangement step starts with picking up some atoms and lasts until dropping off the last atoms."

- Routing-aware placement: A placement strategy that anticipates routing constraints to maximize parallel movements and reduce rearrangement steps. "the state-of-the-art compiler~\cite{stadeRoutingAwarePlacementZoned2025arxiv} utilizing routing-aware placement improves significantly over previous approaches"

- Rydberg beam: Laser illumination used to excite atoms to Rydberg levels for blockade-mediated interactions. "When illuminated with the so-called Rydberg beam, it ensures that only qubits within a certain interaction radius of each other interact"

- Rydberg blockade mechanism: A physical effect in which excitation of one atom inhibits excitation of nearby atoms, enabling two-qubit gates. "are realized by the Rydberg blockade mechanism~\cite{everedHighfidelityParallelEntangling2023,bluvsteinLogicalQuantumProcessor2023}."

- Rydberg laser: The laser used to excite atoms into Rydberg states across the entanglement zone. "when illuminating the entire entanglement zone with a Rydberg laser, all atoms within that zone are excited to the Rydberg state."

- Rydberg state: A highly excited electronic state of an atom characterized by strong, long-range interactions. "all atoms within that zone are excited to the Rydberg state"

- Reuse Analysis: A compilation analysis that identifies atoms that can stay in the entanglement zone across layers to reduce movement. "Reuse Analysis, proposed in~\cite{linReuseAwareCompilationZoned2024}, reduces rearrangement overhead by identifying atoms that can remain in the entanglement zone across multiple layers."

- Reuse-aware compilation: A methodology that incorporates reuse decisions during compilation to improve fidelity and reduce overhead. "it introduces reuse-aware compilation to further improve the overall quantum circuit fidelity."

- Spatial Light Modulator (SLM): A static optical device that creates fixed trap arrays for storing atoms. "static Spatial Light Modulator~(SLM) traps that hold the atoms in place"

- Storage zone: A region with long coherence times where non-interacting qubits are kept to minimize errors. "storage zones featuring long coherence times"

- Strict routing: The conventional routing approach that maintains row/column order and avoids intermediate reordering. "Using strict routing, four atoms can be moved in one rearrangement step"

- Zoned neutral atom architectures: Neutral-atom quantum computing platforms partitioned into specialized zones (entanglement, storage, measurement). "Zoned neutral atom architectures are emerging as a promising platform for large-scale quantum computing."

Collections

Sign up for free to add this paper to one or more collections.